#### SEE 3223 Microprocessors

## 5: Data Processing Instructions

Muhammad Mun'im Ahmad Zabidi (munim@utm.my)

## **Data Processing Instructions**

- Arithmetic operations:

- ADD, SUB, MULU, MULS, EXT, NEG.

- Logical

- AND, OR, EOR, NOT

- Shift

- ASL, ASR, LSL, LSR, ROL, ROR, ROXL, ROXR.

- Bit operations:

- BCLR, BSET, BCHG, BTST

## **Encoding Integers**

#### **Unsigned**

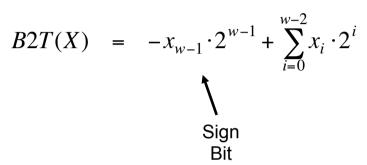

#### Two's Complement

$$B2U(X) = \sum_{i=0}^{w-1} x_i \cdot 2^i$$

|   | Decimal | Hex   | Binary            |  |

|---|---------|-------|-------------------|--|

| Х | 15740   | 3D 7C | 00111101 01111100 |  |

| У | -15740  | C2 84 | 11000010 10000100 |  |

- Sign Bit

- For 2's complement, most significant bit indicates sign

- 0 for nonnegative

- 1 for negative

## **Numeric Ranges**

| Unsigned Values (w = number of bits) |      |      |  |  |  |

|--------------------------------------|------|------|--|--|--|

| Notation Value Binary Pattern        |      |      |  |  |  |

| $U_{min}$                            | 0    | 0000 |  |  |  |

| U <sub>max</sub>                     | 2w-1 | 1111 |  |  |  |

| Two's Com        | Two's Complement Values (w = number of bits) |      |  |  |  |  |

|------------------|----------------------------------------------|------|--|--|--|--|

| Notation         | Notation Value Binary Pattern                |      |  |  |  |  |

| $T_{min}$        | -2 <sup>w-1</sup>                            | 1000 |  |  |  |  |

| T <sub>max</sub> | 2 <sup>w-1</sup> -1                          | 0111 |  |  |  |  |

Values for w = 8

|                  | Decimal | Hex | Binary    |

|------------------|---------|-----|-----------|

| $U_{max}$        | 255     | FF  | 1111 1111 |

| T <sub>max</sub> | +127    | 7F  | 0111 1111 |

| $T_{min}$        | -128    | 80  | 1000 0000 |

| -1               | -1      | FF  | 1111 1111 |

| 0                | 0       | 00  | 0000 0000 |

Values for w = 16

|                         | Decimal Hex Binary                        |                     | Binary              |

|-------------------------|-------------------------------------------|---------------------|---------------------|

| U <sub>max</sub> 65535  |                                           | FF FF               | 1111 1111 1111 1111 |

| $T_{max}$               | T <sub>max</sub> +32767 7F FF 0111 1111 1 |                     | 0111 1111 1111 1111 |

| T <sub>min</sub> -32768 |                                           | 80 00               | 1000 0000 0000 0000 |

| -1 -1 FF FF 111         |                                           | 1111 1111 1111 1111 |                     |

| 0 0 00 00 0000 0000     |                                           | 0000 0000 0000 0000 |                     |

#### Values for Different Word Sizes

Observations

$$|\mathsf{T}_{\mathsf{Min}}| = \mathsf{T}_{\mathsf{Max}} + 1$$

Asymmetric range

$$U_{Max} = 2 * T_{Max} + 1$$

|      | W    |            |                |                            |  |  |  |  |

|------|------|------------|----------------|----------------------------|--|--|--|--|

|      | 8    | 8 16 32 64 |                |                            |  |  |  |  |

| UMax | 255  | 65,535     | 4,294,967,295  | 18,446,744,073,709,551,615 |  |  |  |  |

| TMax | 127  | 32,767     | 2,147,483,647  | 9,223,372,036,854,775,807  |  |  |  |  |

| TMin | -128 | -32,768    | -2,147,483,648 | -9,223,372,036,854,775,808 |  |  |  |  |

#### **ADD**

- Adds the contents of the source location to the contents of a destination location and stores the result in the destination location.

- Source: All addressing modes; however, either source or destination must be a data register.

- Destination: All except immediate, address register direct and program relative.

| Effect on CCR Flags                              |                                                   |  |  |

|--------------------------------------------------|---------------------------------------------------|--|--|

| C Set if a carry is generated, cleared otherwise |                                                   |  |  |

| V Set if an overflow occurred, cleared otherwise |                                                   |  |  |

| Z Set if the result is zero. Cleared otherwise.  |                                                   |  |  |

| N                                                | Set if the result is negative. Cleared otherwise. |  |  |

| Х                                                | Set the same as the carry bit.                    |  |  |

### **SUB**

- Subtraction: SUB src, dest

- $[dest] \leftarrow [dest] [src]$

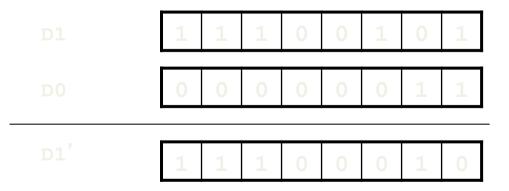

#### SUB.B D0,D1

|                                                  | Effect on CCR Flags                               |  |  |  |

|--------------------------------------------------|---------------------------------------------------|--|--|--|

| C Set if a carry is generated, cleared otherwise |                                                   |  |  |  |

| V Set if an overflow occurred, cleared otherwise |                                                   |  |  |  |

| Z Set if the result is zero. Cleared otherwise.  |                                                   |  |  |  |

| N                                                | Set if the result is negative. Cleared otherwise. |  |  |  |

| Х                                                | Set the same as the carry bit.                    |  |  |  |

## Effect of Arithmetic Operations on CCR

Addition:

V=

$$a_{n-1} \cdot b_{n-1} \cdot s_{n-1} + a_{n-1} \cdot b_{n-1} \cdot s_{n-1}$$

where  $a_{n-1}$ ,  $b_{n-1}$ ,  $s_{n-1}$  are the MSBs of source destination and result, respectively

## Effect of Arithmetic Operations on

Subtraction:

V=  $(a_{n-1} \oplus b_{n-1}) \cdot (\overline{d_{n-1} \oplus a_{n-1}})$ where  $a_{n-1}$ ,  $b_{n-1}$ ,  $d_{n-1}$  are the MSBs of source destination and result, respectively

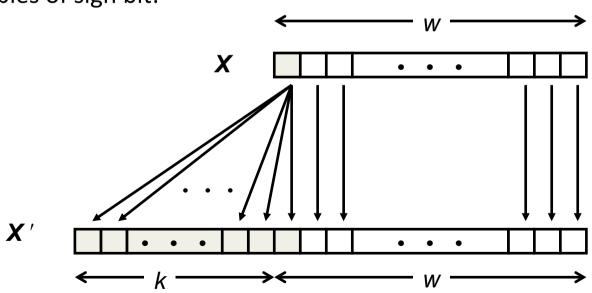

## Sign Extension

- Task:

- Given w-bit signed integer X

- Convert it to w+k-bit integer with same value

- Rule:

- Make k copies of sign bit:

## Sign EXTend Instruction

- Extends the sign bit of the low-order byte or word of a data register:

- EXT.W sign extends the low order byte to 16 bits;

- EXT.L sign extends the low order word to 32 bits.

|              |           | EXT.W D2 | Registers |           |  |

|--------------|-----------|----------|-----------|-----------|--|

| Registers    |           | EXT.W DZ |           | XXXX FFC3 |  |

| D2           | 0000 70C3 |          | D3        | XXXX XXXX |  |

| D3 XXXX XXXX |           |          |           |           |  |

|              |           | EXT.L D2 | Regis     | sters     |  |

|              |           |          | D2        | 0000 70C3 |  |

|              |           |          | D3        | XXXX XXXX |  |

ocw.utm.my

# Example: Adding Different-Sized Numbers

```

* Calculate A = B + C - D

* Where B is a longword, C is a word and D is a byte.

$1000

Program origin

ORG

B,D0

Get B to T (running sum)

START

MOVE L

Get C

MOVE.W

C,D1

Convert C to longword

EXT.L

D1

Add C to T

ADD.L

D1,D0

MOVE . B

D,D2

Get D

EXT.W

D2

Convert D to word

EXT.L

D2

Then convert D to long

SUB.L

D2,D0

Subtract D from T

MOVE L

DO,A

Store T in A

#$2700

Halt processor at end of program

STOP

$1000

ORG

DS.L

A

1

DC.L

В

40

-16

C

DC.W

DC.B

D

END

START

```

\*

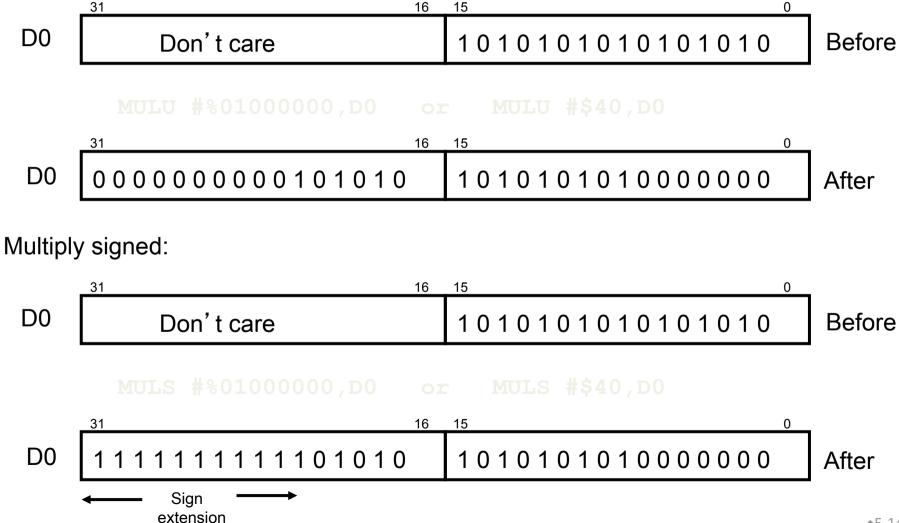

## MULU, MULS Instructions

- MULU performs unsigned multiplication and MULS performs signed multiplication on two's complement numbers.

- Multiplication is a 16-bit operation that multiplies the low-order 16-bit word in Dn (destination data register) by the 16-bit word at the effective address.

The 32-bit results is stored in the full destination data register Dn.

- Source: All modes except address register direct.

- Destination: Data register.

|   | Effect on CCR                                     |  |  |  |

|---|---------------------------------------------------|--|--|--|

| С | Always cleared.                                   |  |  |  |

| V | Always cleared.                                   |  |  |  |

| Z | Set if the result is zero. Cleared otherwise.     |  |  |  |

| N | Set if the result is negative. Cleared otherwise. |  |  |  |

| X | Not affected.                                     |  |  |  |

## MULU, MULS Example

Multiply unsigned:

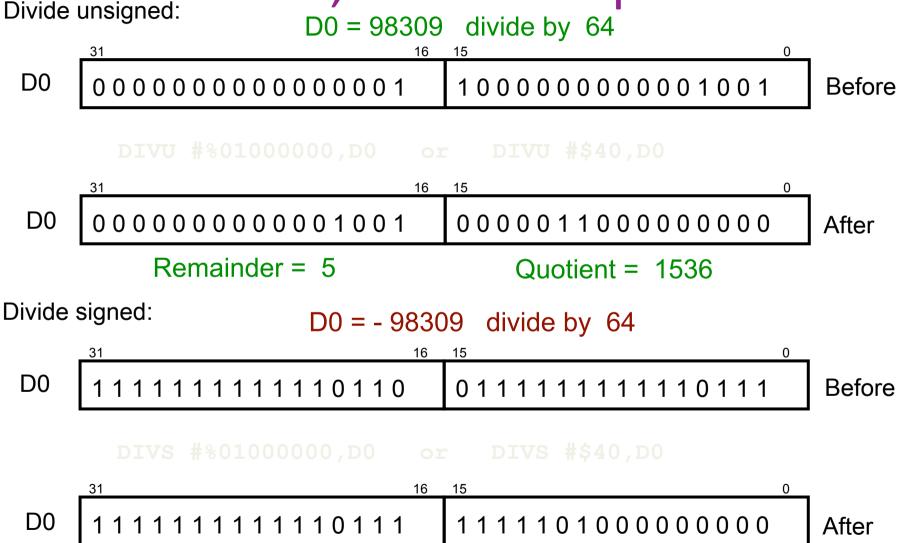

## DIVU, DIVS Instructions

- DIVU performs unsigned division, and DIVS performs signed division on two's complement numbers.

- The 32-bit long word in the data register is divided by the 16-bit word at the effective address.

- The 16-bit quotient is stored in the lower-order word of the register and the remainder is stored in the upper-order word.

- Source: All modes except address register direct.

- Destination: Data register.

Overflow may occur if quotient does not fit in 16 bits

Trap may occur if divide by zero is attempted

| Cuicii u | Always cleared.                                                                                    |

|----------|----------------------------------------------------------------------------------------------------|

| V        | Set if division overflow occurred, cleared otherwise. Undefined if divide by zero occurs.          |

| Z        | Set if the quotient is zero. Cleared otherwise. Undefined if overflow or divide by zero occurs     |

| N        | Set if the quotient is negative. Cleared otherwise. Undefined if overflow or divide by zero occurs |

| Х        | Not affected.                                                                                      |

## DIVU, DIVS Example

Divide unsigned:

Remainder = -5

Quotient = -1536

#### **EXT before DIVS**

- EXT is often used with DIVS, because DIVS requires a 32-bit dividend.

- EXT.L D1 sign-extends the low-order word in D1 to 32 bits by copying D1(15) to bits D1(16:31).

```

MOVE.W (A0),D0 ; load 16-bit dividend from memory EXT.L D0 ; extend to 32 bits DIVS #42,D0 ; perform the division MOVE.W D0,2(A0) ; store the quotient

```

## Negate Instruction

• Negation: negative value or 2's complement

NEG.B D0

#### **SWAP** instruction

- SWAP instruction exchanges the top word with the lower word of a data register

- Useful to get the remainder of a division operation.

#### **EXG** instruction

EXG instruction exchanges a register with another register

D0

89ABCDEF

D1

11223344

Before

EXG D0,D1 or EXG D1,D0

D0

11223344

D1

89ABCDEF

After

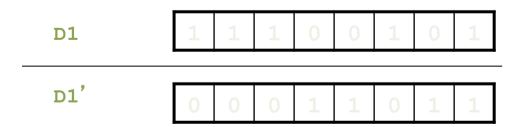

## **Logic Instructions**

• Logic instructions include:

AND Bit-wise ANDOR Bit-wise OR

EOR Bit-wise Exclusive OR

NOT 1's Complement of bits of destination

| Α | В | A AND B | A OR B | A EOR B | NOT A | NOT B |

|---|---|---------|--------|---------|-------|-------|

| 0 | 0 | 0       | 0      | 0       | 1     | 1     |

| 0 | 1 | 0       | 1      | 1       | 1     | 0     |

| 1 | 0 | 0       | 1      | 1       | 0     | 1     |

| 1 | 1 | 1       | 1      | 0       | 0     | 0     |

| Effect on CCR |                                                                          |  |  |

|---------------|--------------------------------------------------------------------------|--|--|

| С             | Always cleared.                                                          |  |  |

| V             | Always cleared.                                                          |  |  |

| Z             | Set if the result is zero. Cleared otherwise.                            |  |  |

| N             | Set if the most significant bit of the result is set; cleared otherwise. |  |  |

| Х             | Not affected.                                                            |  |  |

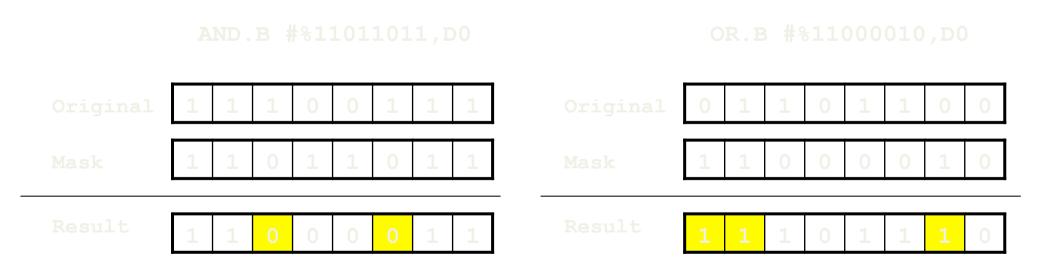

## Masking

- Mask: bit pattern to isolate and manipulate some particular bits

- To set bits, use OR with 1s in the positions of bits to be set.

- Example: Set bits 1, 6, and 7 in D0:

- To clear bits, use AND with 0s in the positions of bits to be cleared.

- Example: Clear bits 2 and 5 in D0:

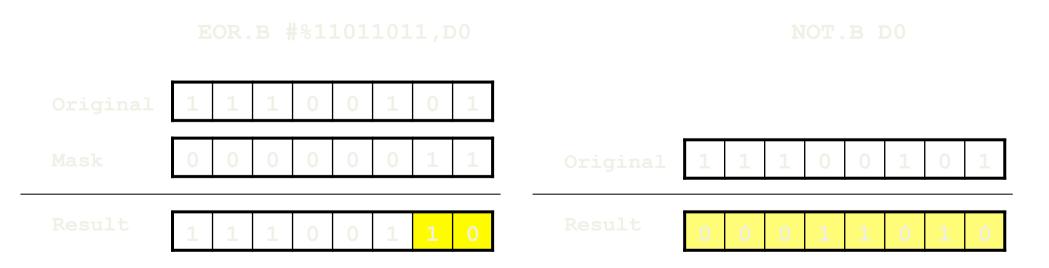

## **Inverting Bits**

- To invert only some bits, use EOR with 1s in the positions of bits to be inverted.

- Example: Invert bits 0 and 1 in D0:

- To invert all bits, use NOT.

- Examples: Inverts all bits in D0

## Practical Application of Logical Ops

Example: A subroutine GetChar inputs an ASCII-encoded character from the keyboard, returns in D1 a 7-bit code plus a parity bit in the MSB. The following sequence will get the character and change the received character to lower-case

```

BSR GetChar

AND.B #%01111111,D1 Clear MSB

OR.B #%00100000,D1 Convert char to lowercase

```

- Note:

- 'A' = 01000001

- 'a' = 01100001

- How about lower-to-upper?

- What if the data is not in A-Z range?

## **ASCII Table**

|      |     | , , , ,       | <i>-</i> |     |              |              |     |              |

|------|-----|---------------|----------|-----|--------------|--------------|-----|--------------|

|      | 000 | 001           | 010      | 011 | 100          | 101          | 110 | 111          |

| 0000 | NUL | DLC           | SP       | 0   | a            | P            | •   | p            |

| 0001 | SOH | DC1           | !        | 1   | A            | Q            | a   | q            |

| 0010 | STX | DC2           | **       | 2   | $\mathbf{B}$ | $\mathbf{R}$ | b   | r            |

| 0011 | ETX | DC3           | #        | 3   | $\mathbf{C}$ | ${f S}$      | c   | S            |

| 0100 | EOT | DC4           | \$       | 4   | D            | $\mathbf{T}$ | d   | t            |

| 0101 | ENQ | NAK           | %        | 5   | ${f E}$      | $\mathbf{U}$ | e   | u            |

| 0110 | ACK | SYN           | &        | 6   | ${f F}$      | $\mathbf{V}$ | f   | V            |

| 0111 | BEL | <b>ETB</b>    | •        | 7   | $\mathbf{G}$ | $\mathbf{W}$ | g   | $\mathbf{W}$ |

| 1000 | BS  | CAN           | (        | 8   | $\mathbf{H}$ | $\mathbf{X}$ | h   | X            |

| 1001 | HT  | $\mathbf{EM}$ | )        | 9   | I            | $\mathbf{Y}$ | i   | y            |

| 1010 | LF  | <b>SUB</b>    | *        | •   | J            | $\mathbf{Z}$ | j   | Z            |

| 1011 | VT  | <b>ESC</b>    | +        | ;   | K            | [            | k   | {            |

| 1100 | FF  | FS            | •        | <   | ${f L}$      | \            | 1   |              |

| 1101 | CR  | GS            | -        | =   | $\mathbf{M}$ | ]            | m   | }            |

| 1110 | SO  | RS            | •        | >   | $\mathbf{N}$ | ^            | n   | ~            |

| 1111 | SI  | US            | /        | ?   | O            | _            | 0   | DEL          |

|      | •   |               |          |     |              |              |     |              |

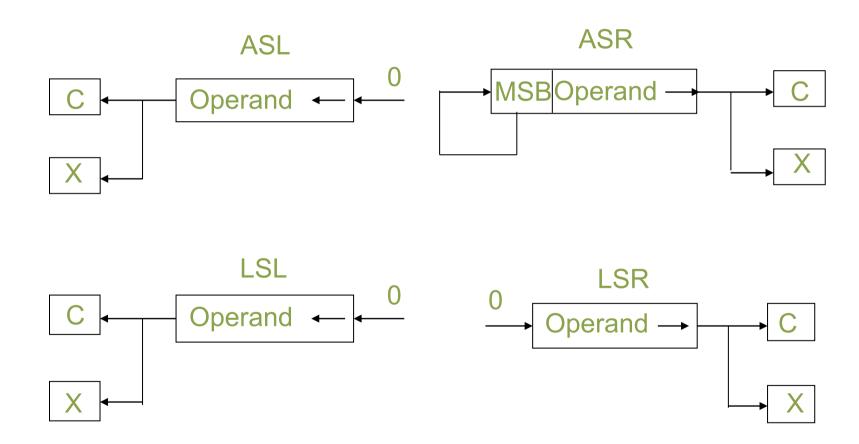

## **Shift Operations**

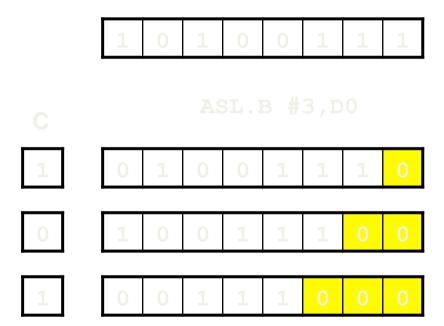

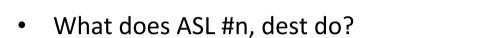

## ASR (Arithmetic Shift Left) Instruction

- The arithmetic shift left operation ASL moves the bits of the operand

- Immediate: in the range 1 to 8

- Register: by the value in a source data register modulo 64

- As each bit is shifted left, it is stored in the Carry flag of the CCR.

- The vacant spot on the right is filled with a zero.

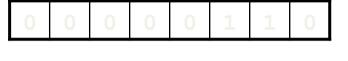

## Why is ASL useful?

- How to multiply D0 by 4?

- ASL is the fastest way to perform "multiply by 2's power"

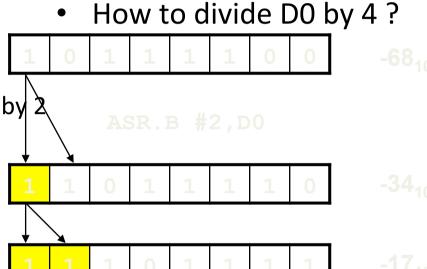

# ASR (Arithmetic Shift Right) Instruction

- Same as ASL, but

- bits shifted to RIGHT

- MSB is duplicated back into MSB (Why?)

- ASR.B #1,D0 is equivalent to dividing D0 by

## **Logical Shift Instructions**

- Two variants:

- LSL (Logical Shift Left)

- LSR (Logical Shift Right)

- Shifts the operand the specified number of positions left/right;

- Immediate: in the range 1 to 8

- Register: by the value in a source data register modulo 64

- Vacated bit positions are always zero-filled

| Effect on CCR |                                                                                                 |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------|--|--|--|

| С             | Set according to the last bit shifted out of the operand. Cleared for a shift count of zero.    |  |  |  |

| V             | Always cleared.                                                                                 |  |  |  |

| Z             | Set if the result is zero. Cleared otherwise.                                                   |  |  |  |

| N             | Set if the result is negative; cleared otherwise.                                               |  |  |  |

| X             | Set according to the last bit shifted out of the operand. Unaffected for a shift count of zero. |  |  |  |

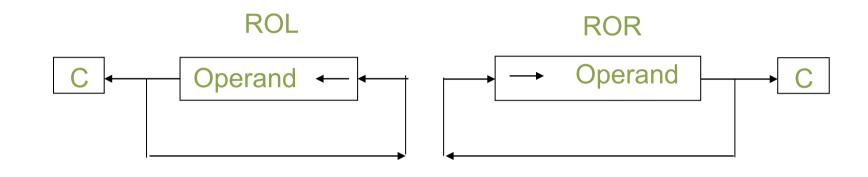

## **Rotate Operations**

### **Rotate Instructions**

- Two variants:

- ROL(Rotate Left)

- ROR(Rotate Right)

- Shifts or rotate the operand the specified number of positions left/right. Bits

that move off one end are put back on the opposite end after setting or clearing

the C-bit.

- Rotates the operand the specified number of positions left/right;

Immediate: in the range 1 to 8

Begister: by the value in a source data register modulo 64

C Set according to the last bit rotated out of the operand. Cleared when the rotate count is zero.

V Always cleared.

Z Set if the result is zero. Cleared otherwise.

N Set if the most significant bit is set; cleared otherwise.

X Not affected

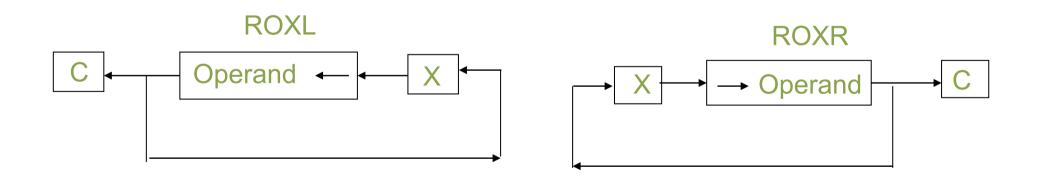

### Rotate with eXtend Instructions

- Two variants:

- ROXL(Rotate Left with eXtend)

- ROXR(Rotate Right with eXtend)

- Rotates the operand the specified number of positions left/right including the Xbit.

- Rotates the operand the specified number of positions left/right;

- Immediate: in the range 1 to 8

- Register: by the value in a source data register modulo 64

| Effect on CCR |                                                                                                                              |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| С             | Set according to the last bit rotated out of the operand. When the rotate count is zero, set to the value of the extend bit. |  |  |

| V             | Always cleared.                                                                                                              |  |  |

| Z             | Set if the result is zero. Cleared otherwise.                                                                                |  |  |

| N             | Set if the most significant bit is set; cleared otherwise.                                                                   |  |  |

| Х             | Set according to the last bit rotated out of the operand. Unaffected for a rotate count of zero.                             |  |  |

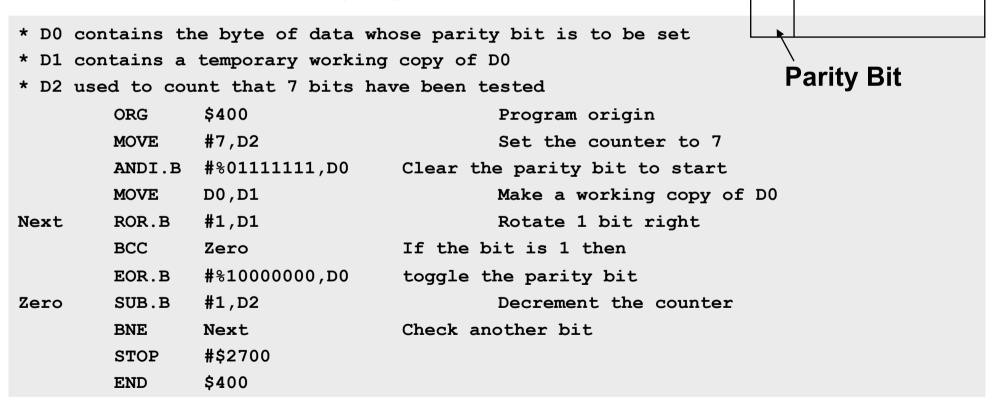

## Example: Setting Parity Bit of A Byte

The following program sets the parity bit (msb) of a byte depending on the number of 1's in the byte using rotate.

If number of coasis add parity bit is set(-1) atherwise - 0

If number of ones is odd parity bit is set( = 1), otherwise = 0

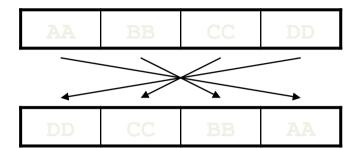

## Big-Endian to Little-Endian Conversion

#### **Graphical Problem Statement**

MOVE.L D0,D1

ROL.L #8,D0

ROR.L #8,D1

AND.L #\$00FF00FF,D0

AND.L #\$FF00FF00,D1

OR.L D1,D0

| D0 |    |    |    |  |  |

|----|----|----|----|--|--|

| AA | BB | CC | DD |  |  |

| AA | BB | CC | DD |  |  |

| BB | CC | DD | AA |  |  |

| BB | CC | DD | AA |  |  |

| 00 | CC | 00 | AA |  |  |

| 00 | CC | 00 | AA |  |  |

| DD | CC | BB | AA |  |  |

DO

| AA | BB | CC | DD |

|----|----|----|----|

| AA | BB | CC | DD |

| DD | AA | BB | CC |

| DD | AA | BB | CC |

| DD | 00 | BB | 00 |

| DD | 00 | BB | 00 |

D1

## Bit Manipulation Instructions

- The 68000 four instruction that manipulate single bits:

- BSET Sets the specified bit to 1.

- BCLR Sets the specified bit to 0.

- BCHG Toggles (inverts) the specified bit.

- BTST Tests the value of a bit. If zero, the Z-flag is set.

- The bit number for this operation can be specified in one of two ways:

- Immediate: e.g. #0, #1, #2, ...

- Register: The specified data register contains the position of the bit to be manipulated.

- Operations are performed on:

- 1 bit of a byte if the operand is in memory or

- 1 bit of a long word if the operand is a data register. Thus:

- No instruction extension is required.

## Bit Operations

Some bit operations (not all) can be implemented using logical operations with masks.

```

BCLR #4,D0 ; same as AND.B #%11101111,D0

BSET #4,D0 ; same as OR.B #%00010000,D0

BCHG #4,D0 ; same as EOR.B #%00010000,D0

BTST #4,D0 ; almost the same as AND.B #%00010000,D0

; but D0 is not destroyed

; If bit 4 is zero, then the Z-bit of

; CCR is set to 1.

```