# SEE 3243 Digital System

Lecturers : Muhammad Mun'im Ahmad Zabidi Muhammad Nadzir Marsono Kamal Khalil

Week 6: Arithmetic Circuits II — CLA, Comparators, ALU, Multiplier

ocw.utm.m

innovative • entrepreneurial • global

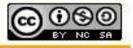

### Full Adder Delay Analysis

From A, B to Co for one stage is 4 delays

From Ci to Co is 2 delays for each subsequent stage or 2n + 2 for n stages

#### **Ripple Carry Adder Analysis**

- Total delay for final sum & carry is 2n+2 gate delays (n = # of stages)

- Assumes XOR is 2 delays

- Delay from C<sub>i</sub> to C<sub>i+1</sub> is 2 gate delays (except stage 0, where delay is 4 units)

# Carry Lookahead Adder Analysis

$6\Delta 5\Delta$

PFA 2Δ G s P  $B_3$ B<sub>2</sub> B<sub>1</sub>  $A_2$ Α. Bo A<sub>3</sub> A.0 PEA PFA PFA PEA 2<u>Λ</u> P1  $c_2 \quad 4\Delta s_1 \quad G_1$  $G_2$ P<sub>2</sub> C. S<sub>0</sub> G<sub>0</sub> Po S<sub>3</sub> G<sub>3</sub>  $\mathsf{P}_3$ S2 Ga Pa C<sub>3</sub> G<sub>2</sub> P<sub>2</sub> C2 G, Ρ, c, G<sub>0</sub> P<sub>0</sub>  $4\Delta$ C<sub>o</sub> 4Δ **4**Δ IG. Carry Lookahead

If we reduce the time to compute  $C_3$ , we can reduce delay to get  $S_3$  (final sum) to 6 gate delays

ocw.utm.my

# **Carry Lookahead Logic Derivation**

Carry Generate  $G_i = A_i B_i$  must generate carry when A = B = 1

Carry Propagate  $P_i = A_i \text{ xor } B_i$

Sum and Carry can be reexpressed in terms of generate/propagate:

$$S_{i} = A_{i} \text{ xor } B_{i} \text{ xor } C_{i} = P_{i} \text{ xor } C_{i}$$

$$C_{i+1} = A_{i} B_{i} + A_{i} C_{i} + B_{i} C_{i}$$

$$= A_{i} B_{i} + (A_{i} + B_{i}) C_{i}$$

$$= A_{i} B_{i} + (A_{i} \text{ xor } B_{i}) C_{i}$$

$$= G_{i} + P_{i} C_{i}$$

# Carry Lookahead Logic

• Reexpress the carry logic as follows:

$$C_{1} = G_{0} + P_{0} C_{0}$$

$$C_{2} = G_{1} + P_{1} C_{1}$$

$$= G_{1} + P_{1} G_{0} + P_{1} P_{0} C_{0}$$

$$C_{3} = G_{2} + P_{2} C_{2}$$

$$= G_{2} + P_{2} G_{1} + P_{2} P_{1} G_{0} + P_{2} P_{1} P_{0} C_{0}$$

$$C4 = G_{3} + P_{3} C_{3}$$

$$= G_{3} + P_{3} G_{2} + P_{3} P_{2} G_{1} + P_{3} P_{2} P_{1} G_{0} + P_{3} P_{2} P_{1} P_{0} C_{0}$$

• Variables are the adder inputs and C<sub>0</sub> (carry in to stage 0)!

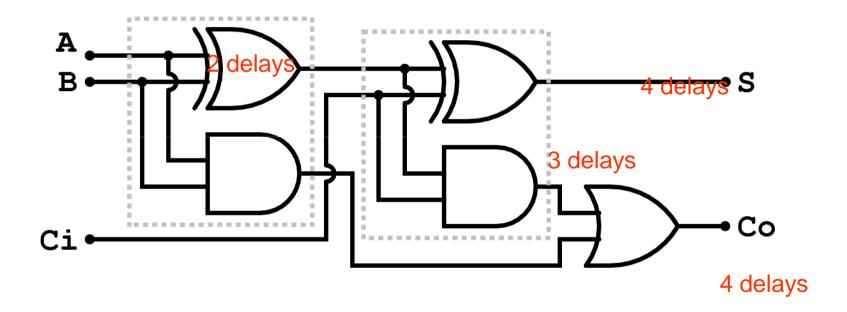

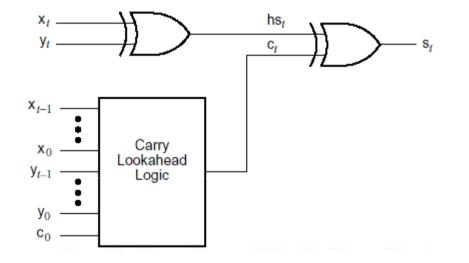

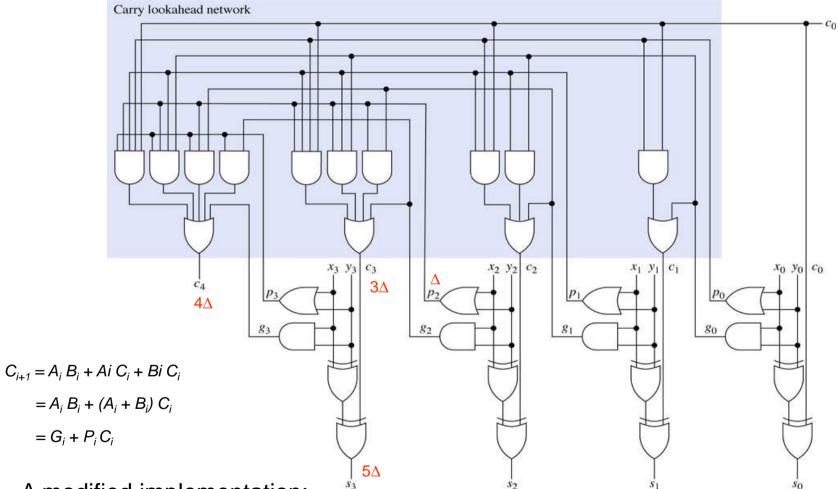

#### Structure of One Stage in CLA

- To compute  $S_i$ , only  $x_{i-1} \dots x_0$ ,  $y_{i-1} \dots y_0$  and  $c_0$  are needed.

- No need to wait for c<sub>i-1</sub>

#### Alternative CLA Design

A modified implementation:

P<sub>i</sub> computed using OR gates (slightly faster)

6-9

- S3

- S2

- S0

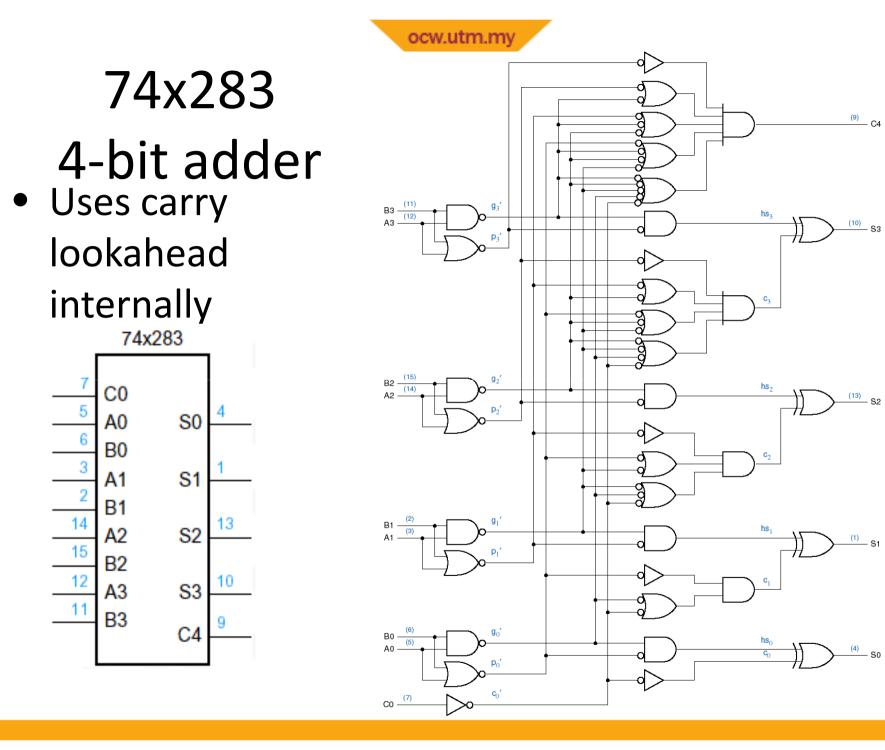

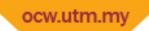

### Cascading CLA

• Similar to ripple adder, but different latency

Delay of each stage is 4 gate levels instead of 10 for ripple adders

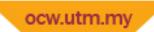

### **Hierarchical Carry Lookahead**

- Second level carry lookahead unit extends lookahead to 16 bits

- If extended to 64 bits reduces gate delay from 130 to 14, or improved by a factor of 9 6-11

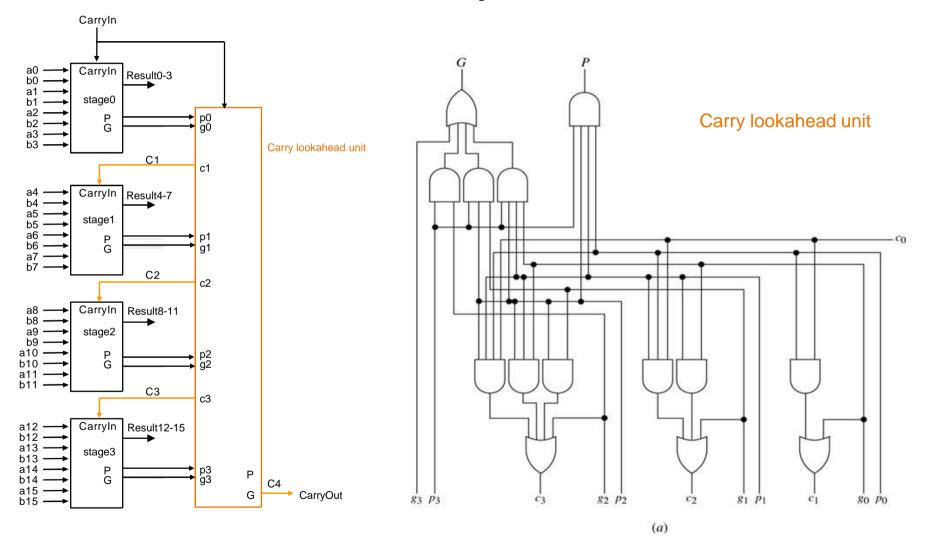

# Carry Select Adder

- Redundant hardware to make carry calculation go faster

- Compute the high order sums in parallel

- one addition assumes carry in = 0

- the other assumes carry in = 1

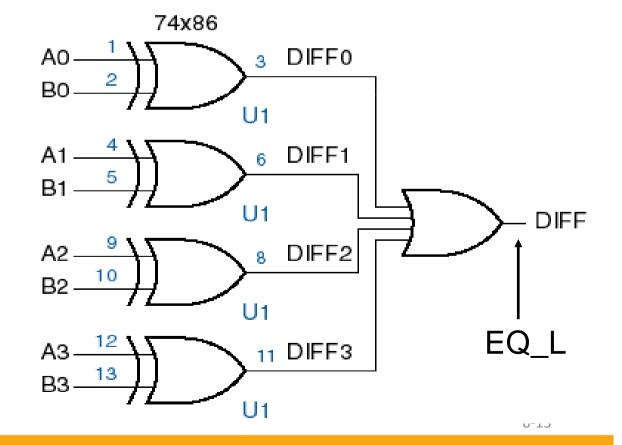

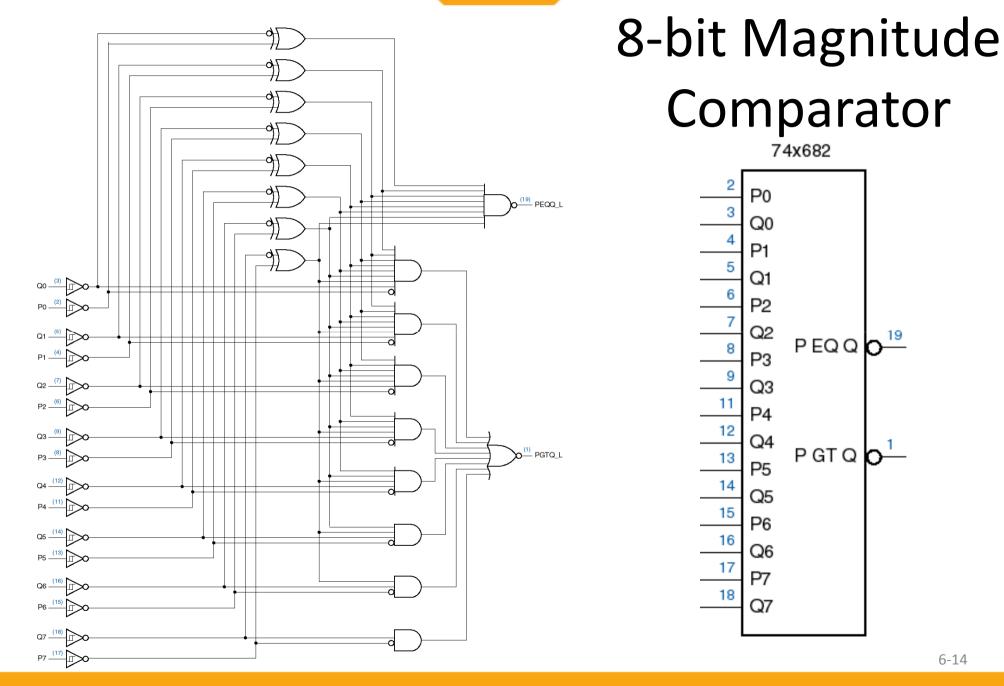

# Equality Comparators

1-bit comparator

4-bit comparator

ocw.utm.my

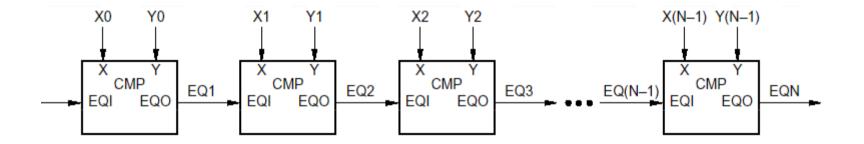

#### **Iterative Comparator**

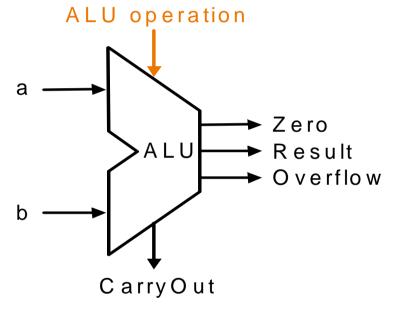

# Arithmetic Logic Unit

- Basic building block of every CPU.

- Combinational circuit.

- Does integer addition, subtraction.

- Also does all 16 bitwise logical operations.

- Does not do multiply, divide. They would be implemented either by a separate unit, or subroutines (slow but cheap).

- Floating operations are also one or more separate units. (More: faster, costlier.)

- Why combine arithmetic & logic? They share a lot of circuitry.

Common symbol for ALU

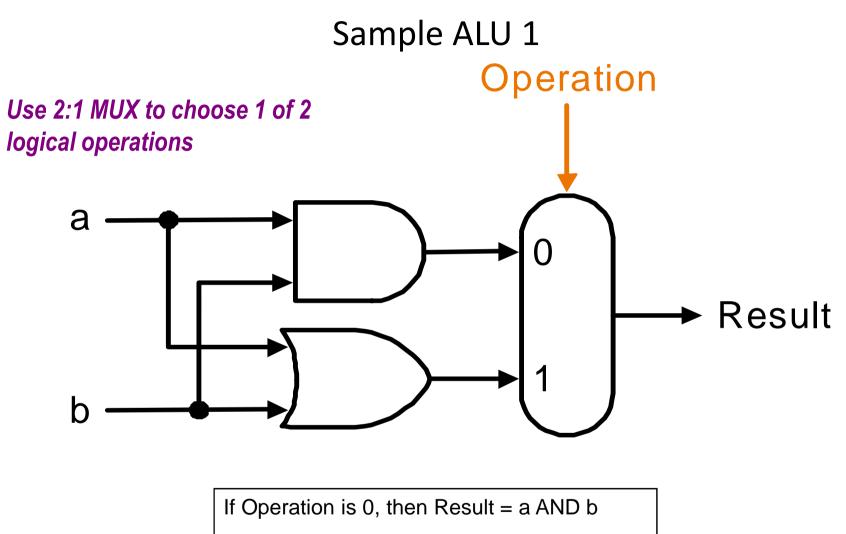

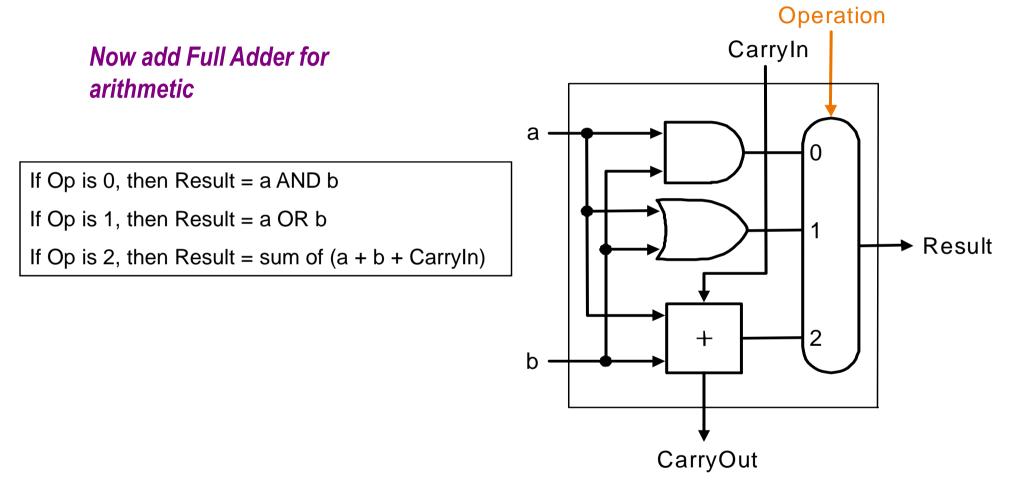

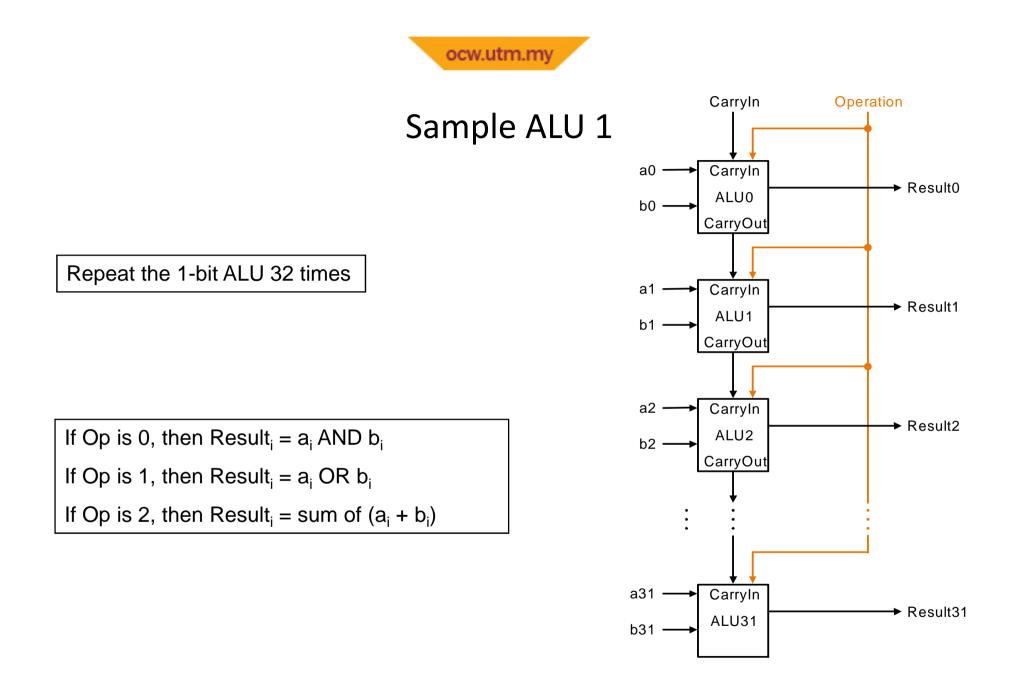

#### Sample ALU 1: Mux Approach

1. AND gate (c = a . b)

| а | b | c = a . b |  |  |

|---|---|-----------|--|--|

| 0 | 0 | 0         |  |  |

| 0 | 1 | 0         |  |  |

| 1 | 0 | 0         |  |  |

| 1 | 1 | 1         |  |  |

Start with Simple Logical Operations

2. OR gate (c = a + b)

| а | b | c = a + b |

|---|---|-----------|

| 0 | 0 | 0         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 1         |

If Operation is 1, then Result = a OR b

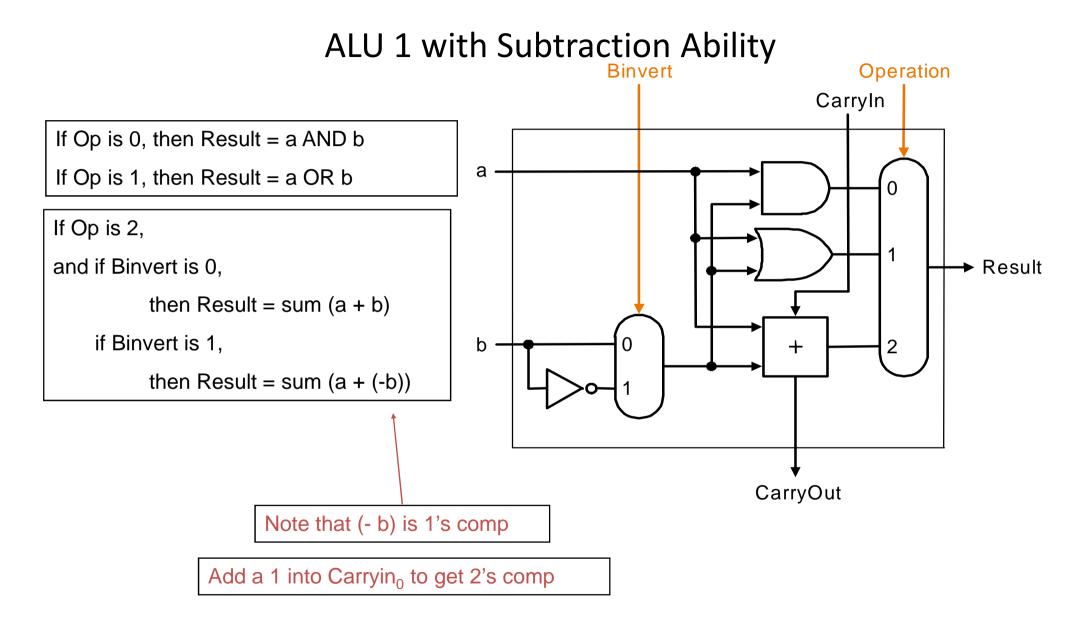

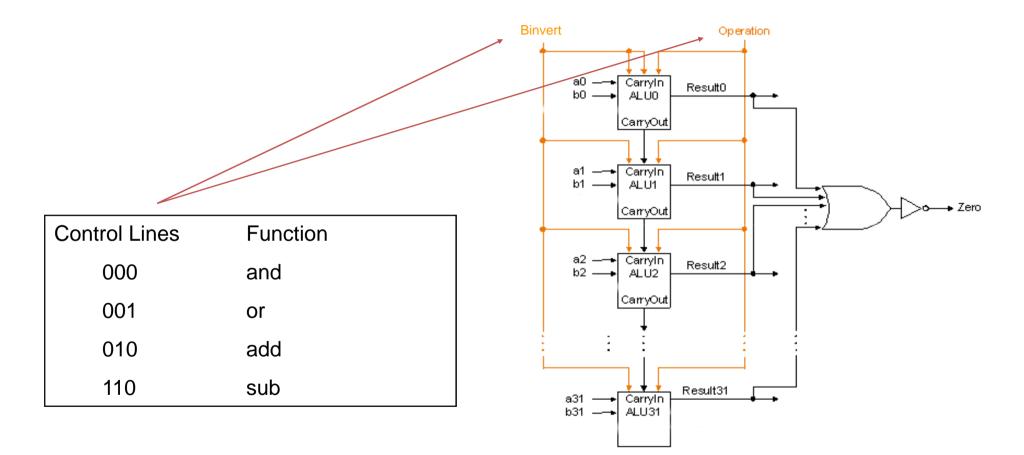

#### Sample ALU 1

#### ALU 1 with Zero Detection

# Sample ALU 2: Truth Table Approach

We want to design an ALU which can do the following operations:

| m <sub>1</sub> | m <sub>0</sub> | Operation |

|----------------|----------------|-----------|

| 0              | 0              | A plus B  |

| 0              | 1              | A minus B |

| 1              | 0              | A plus 1  |

| 1              | 1              | A nor B   |

Assume inputs A and B are 4-bit 2's complement numbers, and F is output.

One way of obtaining the circuit is by creating the truth table:

| m1     | m0     | a3     | a2     | a1     | a0     | b3     | b2     | b1     | b0     | f3     | f2     | f1     | f0     | A plus B |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------|

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |          |

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      | 1      |          |

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      | 1      | 0      |          |

| 1<br>1 | 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>0 | A nor B  |

A huge truth table. Imagine truth table for 8-bit inputs!

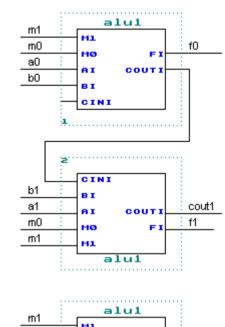

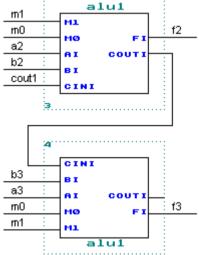

### Sample ALU 2

- Design a universal logic block (called a bit slice) that accepts only 1-bit of the inputs (per logic block).

- We then copy and connect this bit slice as many times as there are input bits.

| m <sub>1</sub> | m <sub>0</sub> | Operation |

|----------------|----------------|-----------|

| 0              | 0              | A plus B  |

| 0              | 1              | A minus B |

| 1              | 0              | A plus 1  |

| 1              | 1              | A nor B   |

# Sample ALU 2

•

•

lacksquare

| Each bit slice has 5 inp<br>on the right.                           | outs a         | nd 2 (                | outputs. Trutl | n table is |            | m 1 m 0 aibicin i ficouti<br>0 0 0 0 0 0 0 0<br>0 0 1 1 0                                                                                       |

|---------------------------------------------------------------------|----------------|-----------------------|----------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Remember, the bit slic<br>same circuit for all inp                  |                |                       | universal, i.e | . exactly  | A tambah B | 01010<br>01101<br>10010<br>10101                                                                                                                |

| For A plus 1 operation input. But remember, operations require B in | it mu          | •                     | •              |            | 44-1-1-B   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                            |

| Another example: NO input, but the truth ta cini input.             | •              |                       | •              |            | A tolak B  | $1 \ 0 \ 0 \ 01$<br>$1 \ 0 \ 1 \ 11$<br>$1 \ 1 \ 0 \ 10$<br>$1 \ 1 \ 1 \ 01$<br>$1 \ 0 \ 0 \ 0 \ 0 \ 00$<br>$0 \ 0 \ 1 \ 0$<br>$0 \ 1 \ 0 \ 00$ |

|                                                                     | m <sub>1</sub> | m <sub>0</sub>        | Operation      |            | A tambah 1 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                           |

|                                                                     |                | 1 1 0 1 0<br>1 1 1 01 |                |            |            |                                                                                                                                                 |

|                                                                     | 0              | 1                     | A minus B      |            | A NOR B    | 1 100X1X<br>01X0X                                                                                                                               |

A plus 1

A nor B

0

1

1

1

1 X X O X

ocw.utm.my

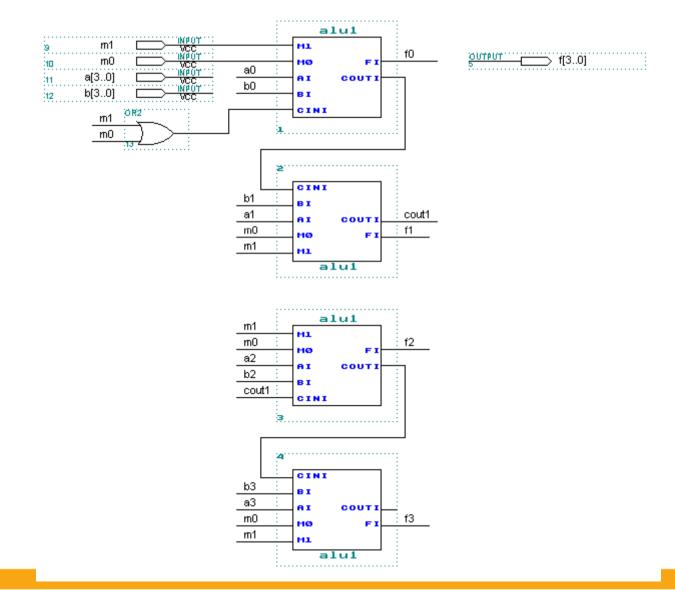

#### Sample ALU 2 Bit Slice Circuit for Sample ALU 2

6-26

ocw.utm.my

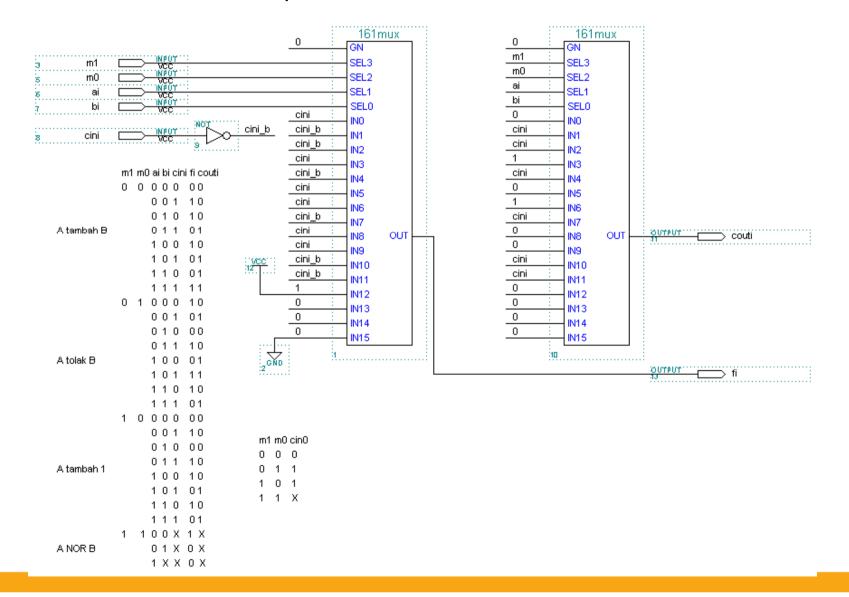

#### Sample ALU 2 Circuit for Sample ALU 2 for 4-Bit Inputs

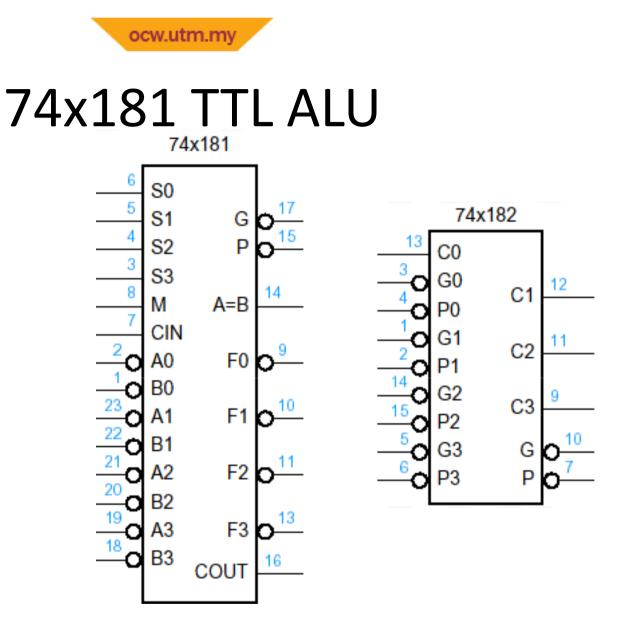

#### 74x181 TTL ALU

| Selection M = 1 |    |    |    | M = 1           | M = 0, Arithm              | etic Functions                    |

|-----------------|----|----|----|-----------------|----------------------------|-----------------------------------|

| S3              | S2 | S1 | S0 | Logic Function  | Cn = 0                     | Cn = 1                            |

| 0               | 0  | 0  | 0  | F = not A       | F = A minus 1              | F = A                             |

| 0               | 0  | 0  | 1  | F = A nand B    | F = A B minus 1            | F = A B                           |

| 0               | 0  | 1  | 0  | F = (not A) + B | F = A (not B) minus 1      | F = A (not B)                     |

| 0               | 0  | 1  | 1  | F = 1           | F = minus 1                | F = zero                          |

| 0               | 1  | 0  | 0  | F = A nor B     | F = A plus (A + not B)     | F = A plus (A + not B) plus 1     |

| 0               | 1  | 0  | 1  | F = not B       | F = A B plus (A + not B)   | F = A B plus (A + not B) plus 1   |

| 0               | 1  | 1  | 0  | F = A xnor B    | F = A minus B minus 1      | F = (A + not B) plus 1            |

| 0               | 1  | 1  | 1  | F = A + not B   | F = A + not B              | F = A minus B                     |

| 1               | 0  | 0  | 0  | F = (not A) B   | F = A plus (A + B)         | F = A plus (A + B) plus 1         |

| 1               | 0  | 0  | 1  | F = A  xor  B   | F = A plus B               | F = A plus B plus 1               |

| 1               | 0  | 1  | 0  | F = B           | F = A (not B) plus (A + B) | F = A (not B) plus (A + B) plus 1 |

| 1               | 0  | 1  | 1  | F = A + B       | F = (A + B)                | F = (A + B) plus 1                |

| 1               | 1  | 0  | 0  | F = 0           | F = A                      | F = A plus A plus 1               |

| 1               | 1  | 0  | 1  | F = A (not B)   | F = A B plus A             | F = AB plus A plus 1              |

| 1               | 1  | 1  | 0  | F = A B         | F= A (not B) plus A        | F = A (not B) plus A plus 1       |

| 1               | 1  | 1  | 1  | F = A           | F = A                      | F = A plus 1                      |

Due to arithmetic equivalence, active HIGH or active LOW input and outputs are available!

Not all operations useful, but fall out when doing the useful ones

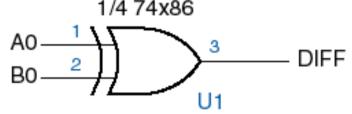

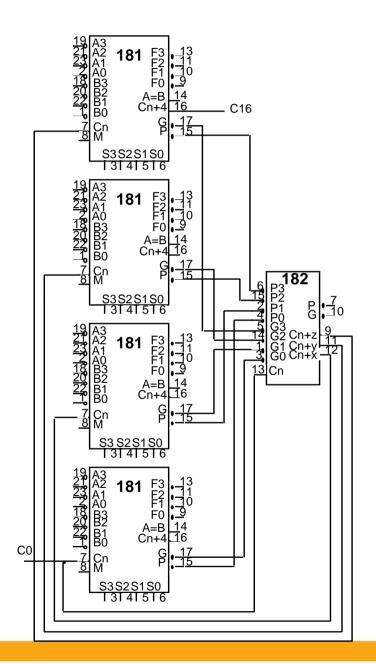

# 16-bit ALU with Carry Lookahead Unit

CLA unit speeds up calculations of multi-chip ALU

6-30

#### 74x381 and 74x382 ALUs

|    |        |    |                                | 74x38          | 1          | 74x382        |

|----|--------|----|--------------------------------|----------------|------------|---------------|

|    | Inputs |    |                                | 5 S0           |            | 5 S0          |

| S2 | S1     | S0 | Function                       | 6 S1<br>7 S2   | G 0 13     |               |

| 0  | 0      | 0  | F = 0000                       | 15CIN          | P <b>p</b> |               |

| 0  | 0      | 1  | F = B minus A minus 1 plus CIN | A0             | F0         | A0 F0         |

| 0  | 1      | 0  | F = A minus B minus 1 plus CIN | B0<br>A1       | F1 9       | B0<br>1 A1 F1 |

| 0  | 1      | 1  | F = A plus B plus CIN          | 2 B1           |            | 2 B1          |

| 1  | 0      | 0  | $F = A \oplus B$               |                | F2 11      |               |

| 1  | 0      | 1  | F = A + B                      |                |            | 10 B2         |

| 1  | 1      | 0  | $F = A \cdot B$                | 17 A3<br>16 B3 | F3         | A3 F3         |

| 1  | 1      | 1  | F = 1111                       | 55             |            | - 50          |

- Compared to 74x181, these ALUs encode their select inputs more compactly, and provide only eight different but useful functions

- The difference?

- 74x381 provides group carry lookahead outputs

- 74x382 provides ripple carry-out and overflow outputs

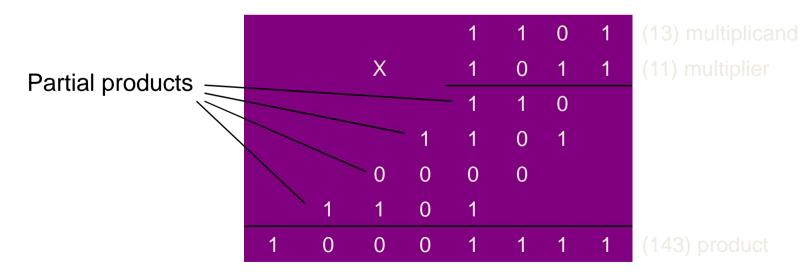

# **Combinational Multiplier**

- Product of 2 4-bit numbers is an 8-bit number

- Product of m-bit x nbit numbers is an (m+n)-bit number

|                       |          |          |          | $A_3$          | A <sub>2</sub>        | A <sub>1</sub> | A <sub>0</sub> |

|-----------------------|----------|----------|----------|----------------|-----------------------|----------------|----------------|

|                       |          |          |          | $B_3$          | B <sub>2</sub>        | B <sub>1</sub> | B <sub>0</sub> |

|                       |          |          |          | $A_3B_0$       | $A_2B_0$              | $A_1B_0$       | $A_0B_0$       |

|                       |          |          | $A_3B_1$ | $A_2B_1$       | $A_1B_1$              | $A_0B_1$       |                |

|                       |          | $A_3B_2$ | $A_2B_2$ | $A_1B_2$       | $A_0B_2$              |                |                |

|                       | $A_3B_3$ | $A_2B_3$ | $A_1B_3$ | $A_0B_3$       |                       |                |                |

| <b>S</b> <sub>7</sub> | $S_6$    | $S_5$    | $S_4$    | S <sub>3</sub> | <b>S</b> <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> |

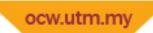

### **Combinational Multiplier**

Fig. 3-33 A 2-Bit by 2-Bit Binary Multiplier

#### Basic Idea of A Larger Multiplier

6-34

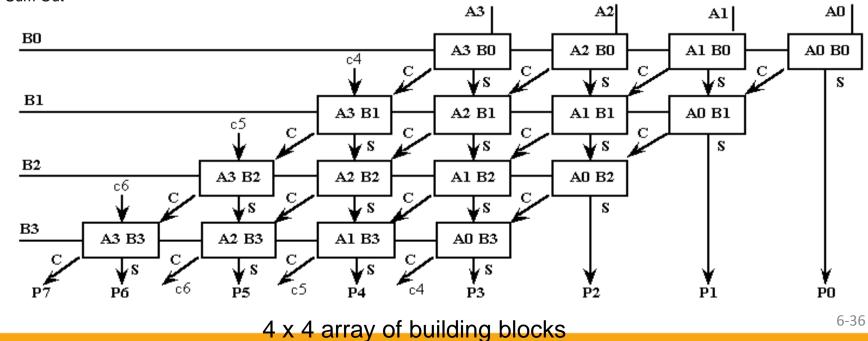

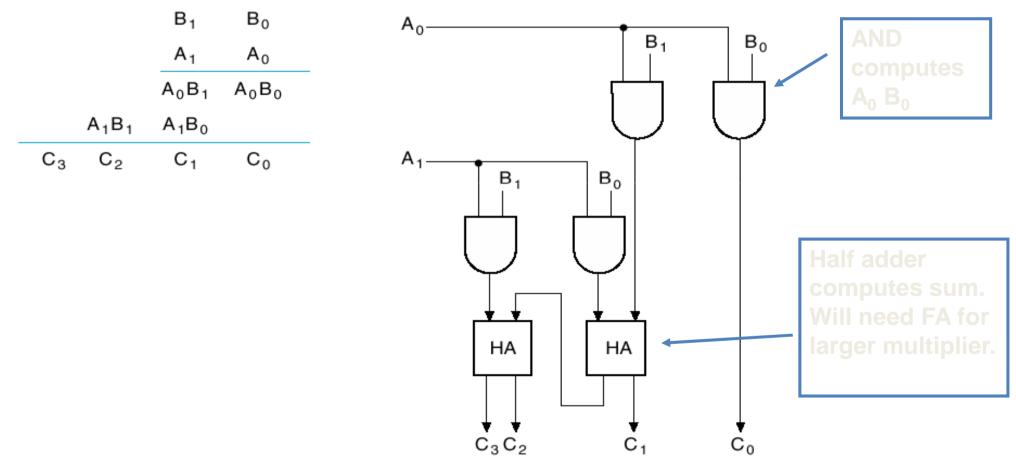

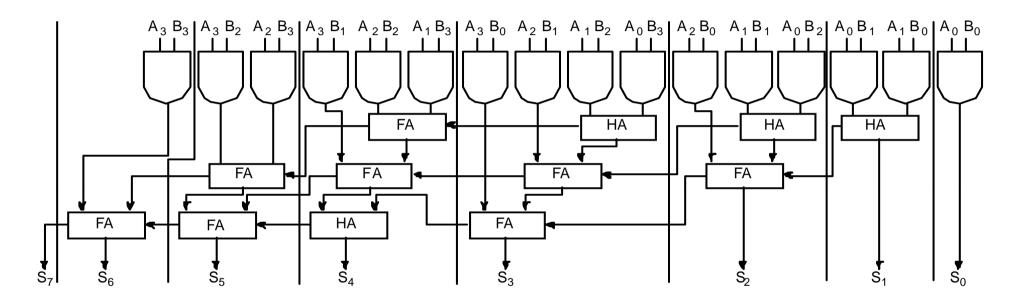

#### 4x4 Combinational Multiplier

Note use of parallel carry-outs to form higher order sums

12 Adders, if full adders, this is 6 gates each = 72 gates

16 gates form the partial products

total = 88 gates!

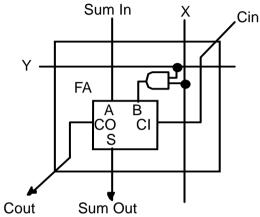

# **Combinational Multiplier**

Another Representation of the Circuit

Building block: full adder + and