#### SEE 3243 Digital System

Lecturers : Muhammad Mun'im Ahmad Zabidi Muhammad Nadzir Marsono Kamal Khalil

#### Week 4:

**Programmable Logic Devices (PLDs)**

innovative • entrepreneurial • global

ocw.utm.my

#### Problems by Using Basic Gates

- Many components on PCB

- As no. of components rise, nodes interconnection complexity grow exponentially

- Growth in interconnection will cause increase in interference, PCB size, PCB design cost, and manufacturing time

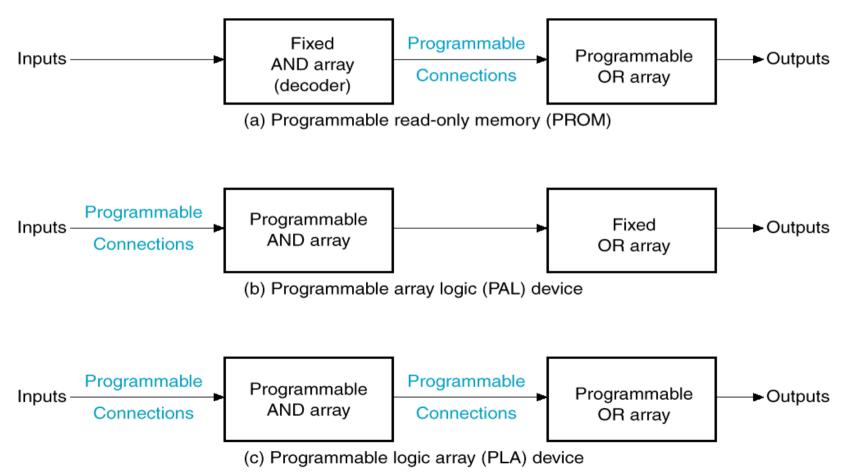

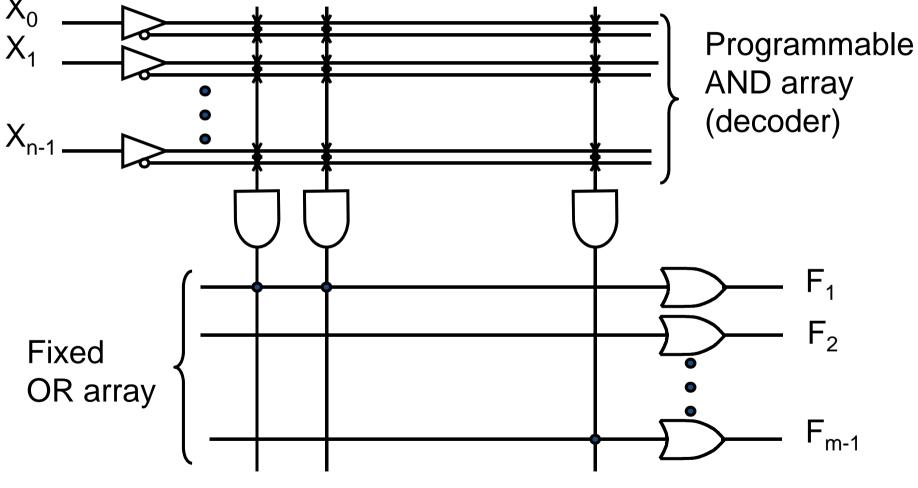

## Types of Programmable Logic Devices

- SPLDs (Simple Programmable Logic Devices)

- ROM (Read-Only Memory)

- PLA (Programmable Logic Array)

- PAL (Programmable Array Logic)

- GAL (Generic Array Logic)

| Device | AND-array    | OR-array     |

|--------|--------------|--------------|

| PROM   | Fixed        | Programmable |

| PLA    | Programmable | Programmable |

| PAL    | Programmable | Fixed        |

| GAL    | Programmable | Fixed        |

# Basic Configuration of Three Simple PLDs

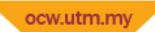

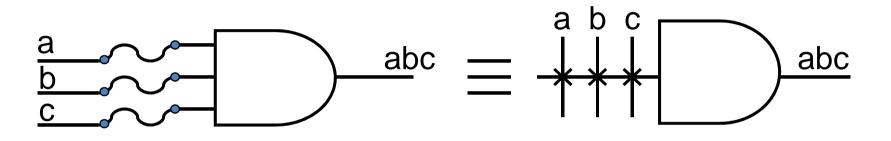

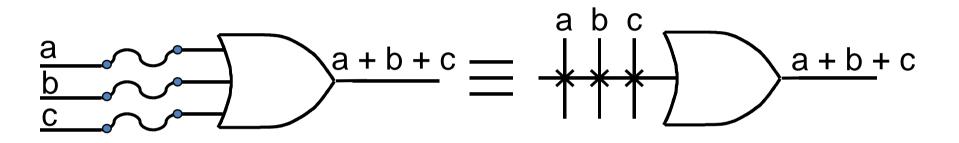

## **AND PLD Notation**

Programming is done by blowing the fuse

AND gate before programming

AND gate after programming

#### **OR PLD Notation**

Programming is done by blowing the fuse

OR gate before programming

OR gate after programming

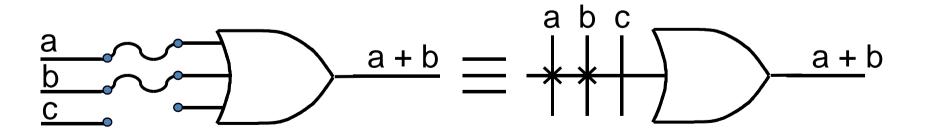

#### **PROM** Notation

#### **PROM Implementation**

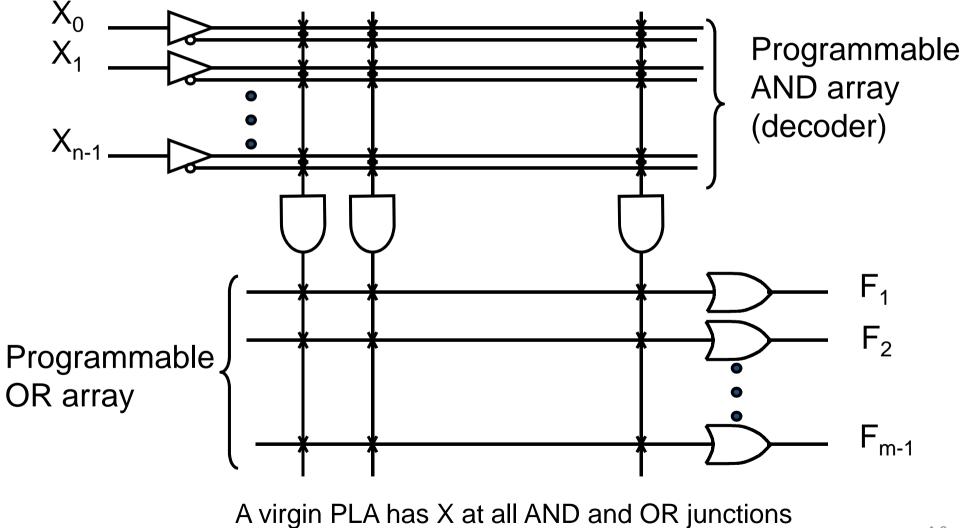

#### **PLA Notation**

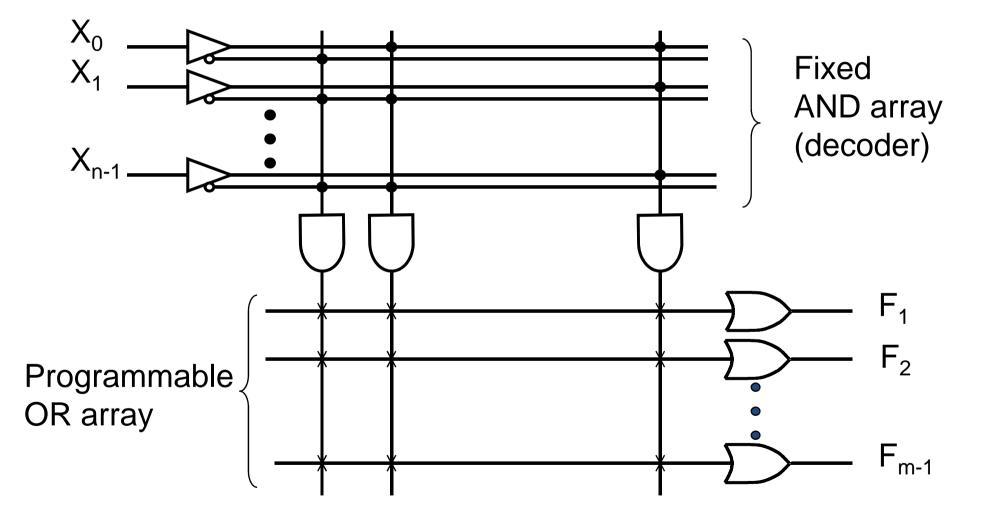

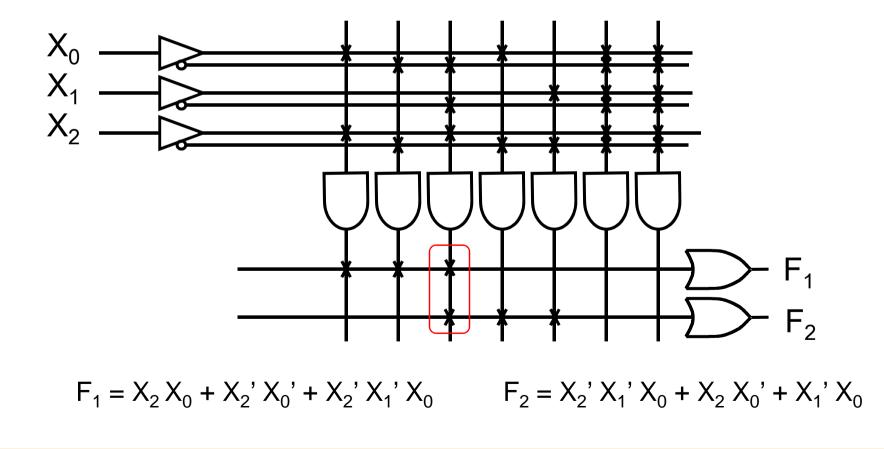

#### **PLA Implementation**

| X <sub>2</sub><br>0 | X <sub>1</sub> | X <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> |

|---------------------|----------------|----------------|----------------|----------------|

| 0                   | 0              | 0              | 1              | 0              |

| 0                   | 0              | 1              | 1              | 1              |

| 0                   | 1              | 0              | 1              | 1              |

| 0                   | 1              | 1              | 0              | 0              |

| 1                   | 0              | 0              | 0              | 1              |

| 1                   | 0              | 1              | 1              | 0              |

| 1                   | 1              | 0              | 0              | 1              |

| 1                   | 1              | 1              | 1              | 0              |

| x2 \ x1x0 | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 0         | 1  | 1  | 0  | 1  |

| 1         | 0  | 1  | 1  | 0  |

$$F_1 = X_2 X_0 + X_2' X_0' + X_2' X_1' X_0$$

reused

| x2 \ x1x0 | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 0         | 0  | 1  | 0  | 1  |

| 1         | 1  | 0  | 0  | 1  |

$$F_2 = X_2 X_0' + X_1 X_0' + X_2' X_1' X_0$$

## **PLA Implementation**

Try to implement both functions using minimum number of total terms (product sharing). Hence  $F_1$  has 3-input term.

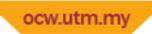

#### **PAL** Notation

Each AND gate is permanently connected to a certain OR gate

#### **PAL Implementation**

| x2 | x1 | x0 | F1 | F2 |

|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 0  |

| 0  | 0  | 1  | 1  | 1  |

| 0  | 1  | 0  | 1  | 1  |

| 0  | 1  | 1  | 0  | 0  |

| 1  | 0  | 0  | 0  | 1  |

| 1  | 0  | 1  | 1  | 0  |

| 1  | 1  | 0  | 0  | 1  |

| 1  | 1  | 1  | 1  | 0  |

| x2 \ x1x0 | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 0         | 1  | 1  | 0  | 1  |

| 1         | 0  | 1  | 1  | 0  |

$F_1 = X_2 X_0 + X_2 X_0 + X_1 X_0$

| x2 \ x1x0 | 00 | 01 | 11 | 10 |

|-----------|----|----|----|----|

| 0         | 0  | 1  | 0  | 1  |

| 1         | 1  | 0  | 0  | 1  |

$$F_2 = X_2' X_1' X_0 + X_2 X_0' + X_1' X_0$$

#### **PAL Implementation**

$F_{1} = X_{2} X_{0} + X_{2} X_{0} + X_{1} X_{0}$   $F_{2} = X_{2} X_{1} X_{0} + X_{2} X_{0} + X_{1} X_{0}$

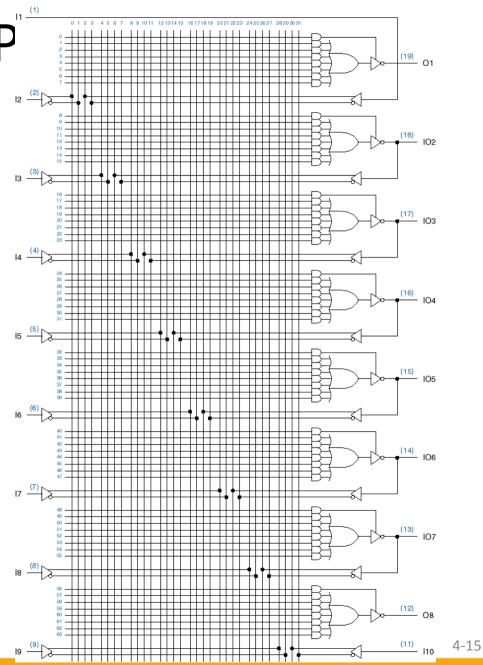

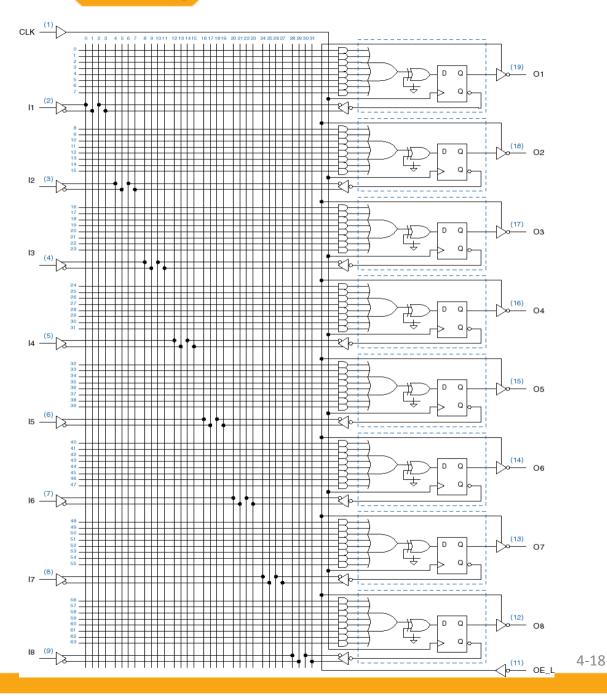

# A Real P

- There're 64 AND gates

- Each AND gate can have 32 inputs (16 variables & complements)

- There're 8 outputs

- Don't count the I/O pins!

- Three common output configs:

- L = pure combinational

- R = registered

- V = macrocell

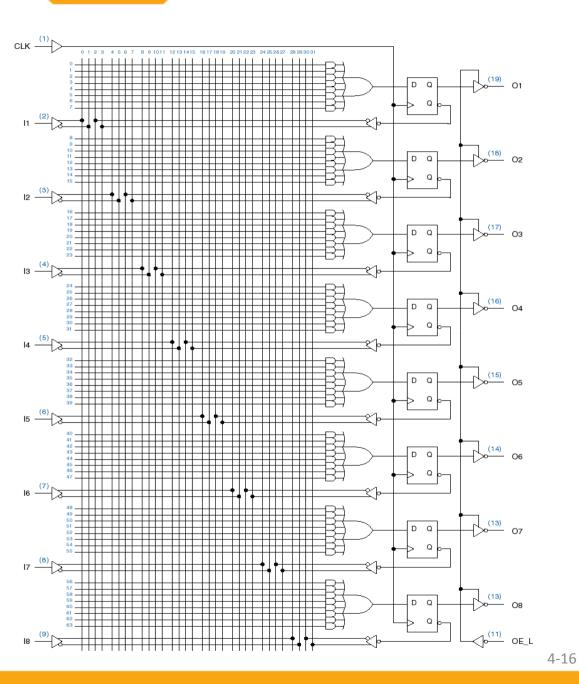

# Sequential PALs

- 16R8

- Notice 8 flip-flops at output

ocw.utm.my

#### GAL (Generic Array Logic)

- GAL can emulate a number of PALs

- No need for PAL anymore!

|                   | PAL                      | GAL                                                |

|-------------------|--------------------------|----------------------------------------------------|

| Device technology | Fuse                     | Electrically erasable cell                         |

| Reconfigurability | One-time<br>programmable | Erasable, reprogrammable                           |

| I/O               | Fixed function           | Selectable: input/output, combinational/registered |

Oh, by the way...

GAL is trademark of Lattice Semiconductor: example GAL22V10 Universal PAL is the trademark of Vantis: example PALCE22V10 (but it's the same thing!) ocw.utm.my

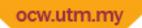

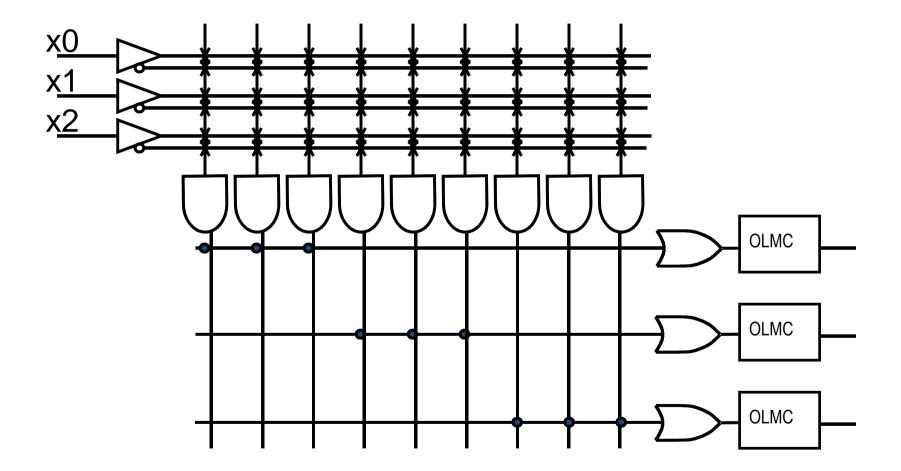

#### GAL16V8

- Each output is programmable as combinational or registered

- Also has programmable output polarity

#### OLMC

- OLMC = Output Logic Macrocell

- Simplified, equivalent circuits:

#### Simplified GAL Representation

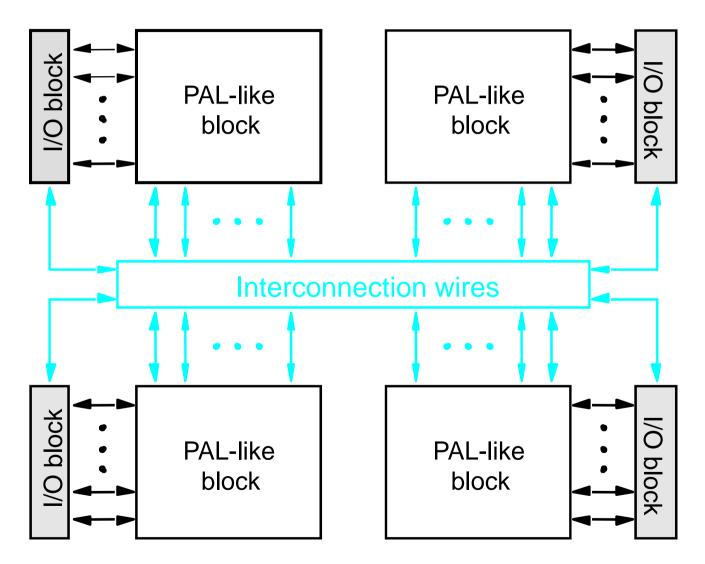

#### PLD programming unit (courtesy of Data IO Corp)

#### **Problems Using SPLD**

- Current trend is

- Increasing gate count

- Increase design complexity

- Requirement for smaller size due to lower cost, lower power and higher reliability

- Fast prototyping for quick design verification

- PROM, PLA and PAL not used much except in small designs!

- Solution:

- CPLD for intermediate complexity

- FPGA for very complex designs (up to millions of gates)

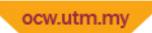

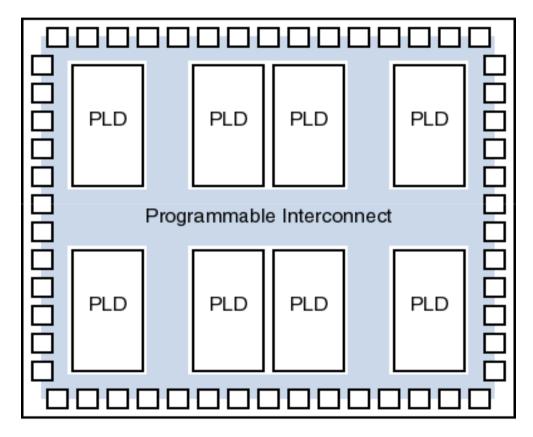

#### Structure of CPLD

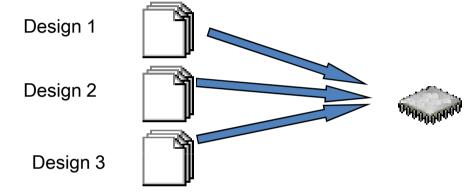

# CPLD Packaging and Programming

(a) CPLD in a Quad Flat Pack (QFP) package

Reduced circuit board space utilization, and significant cost savings

A 44-pin CPLD is equivalent to 600 gates

Some CPLDs have gate equivalents in the millions and over 1000 pins

- Easiest to modify

- Use appropriate CAD tools

- Direct entry of conceptual design into functional circuit

- Streamlined design to prototype process

• Universal inventory, as one IC can be programmed for various applications

• Easy to duplicate

- Reprogrammability

- CPLD can be reprogrammed hundreds of times.

– CPLDs have large amounts of programmable input/output contacts.

- Software and Language

- Manufacturers of CPLDs supply design software (software like Altera Quartus II is a free download)

- VHDL is a standards-based language that most manufacturers conform to

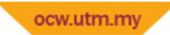

- Simple Interface

- Devices can be interfaced directly to a computer with a serial or USB connection

- In-circuit modifications

- With the proper interface connections, the CPLD logic can be edited incircuit

- Transportable design

- As a designer you may easily exchange your designs and design modifications (e-mail, CD, web site, etc. ...)

#### **CPLDs and FPGAs**

CPLD

FPGA

Complex Programmable Logic Device

| Architecture | PAL/22V10-like<br>More Combinational      |

|--------------|-------------------------------------------|

| Density      | Low-to-medium<br>0.5-10K logic gates      |

| Performance  | Predictable timing<br>Up to 250 MHz today |

| Interconnect | "Crossbar Switch"                         |

Field-Programmable Gate Array

Gate array-like More Registers + RAM

Medium-to-high 1K to 1M system gates

Application dependent Up to 150 MHz today

Incremental

#### CPLDs vs. FPGAs

• CPLD architecture

= input/output block

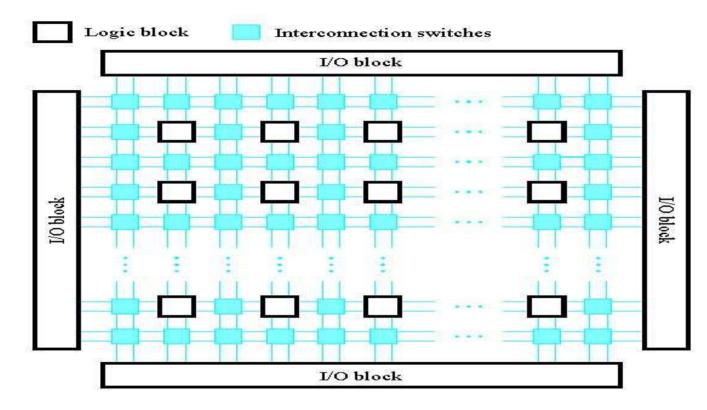

#### **FPGA** architecture

- Much larger number of smaller programmable logic blocks.

- Xilinx calls them CLB (Configurable Logic Block)

- Altera calls them LAB (Logic Array Block) and EAB (Embedded Array Block)

- Embedded in a sea of lots and lots of programmable interconnects.

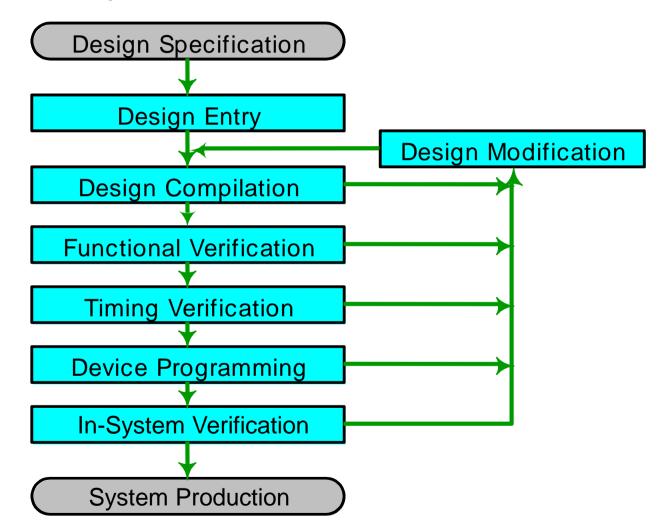

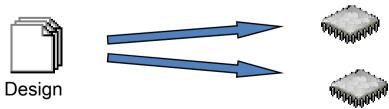

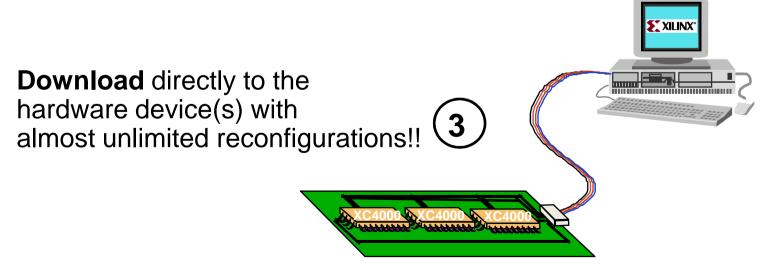

#### **Design Flow**

Design Entry in schematic and/or HDL (ABEL, VHDL, Verilog). Vendors include Altera, Synopsys, Aldec (Xilinx Foundation), Mentor Graphics, Cadence, Viewlogic, etc.

**Implementation** includes Placement & Routing. Also, analyze timing, view layout, and more.

#### **Development Process**