# Digital Electronics (SKEE1223) Digital Integrated Circuits

Muhammad Arif Abd Rahim Muhammad Mun'ím Ahmad Zabidi Ab Hadi Abd Rahman

**Faculty of Electrical Engineering**

UNIVERSITI TEKNOLOGI MALAYSIA innovative • entrepreneurial • global

UTMONLINELEARNING

# Logic Families

# Logic Family Overview

- TTL

- Transistor-Transistor Logic

- Uses bipolar junction transistors (BJT)

- CMOS

- Complimentary Metal Oxide Semiconductor

- Uses Metal Oxide Semiconductor Field Effect Transistors (MOSFET)

- BiCMOS

🐻 UTM

– Combines TTL & CMOS

OUTN

OUTM

## TTL vs CMOS

| TTL                        | CMOS                      |

|----------------------------|---------------------------|

| Inexpensive                | Dissipates low power.     |

| • Draw a lot of power      | Consumption depends on    |

| • Must be supplied with +5 | supply voltage, switching |

| volts                      | frequency, output load    |

| • Each gate usually uses   | and input rise time.      |

| 10mW                       | A typical gate uses only  |

|                            | 10nW.                     |

#### More on CMOS

- CMOS components are more expensive but at the system level, CMOS is less expensive. This is because CMOS chips are smaller and require less power regulation.

- CMOS circuits use almost no power at rest. However, current draw increases with switching frequency.

- CMOS component more likely to be damaged due electrostatic discharge.

#### UTMONLINELEARNING

OUTM

(6 = <mark>-</mark> -

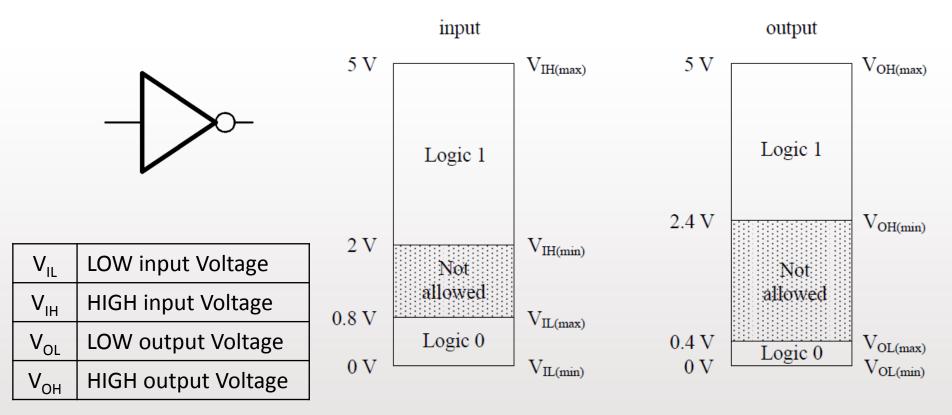

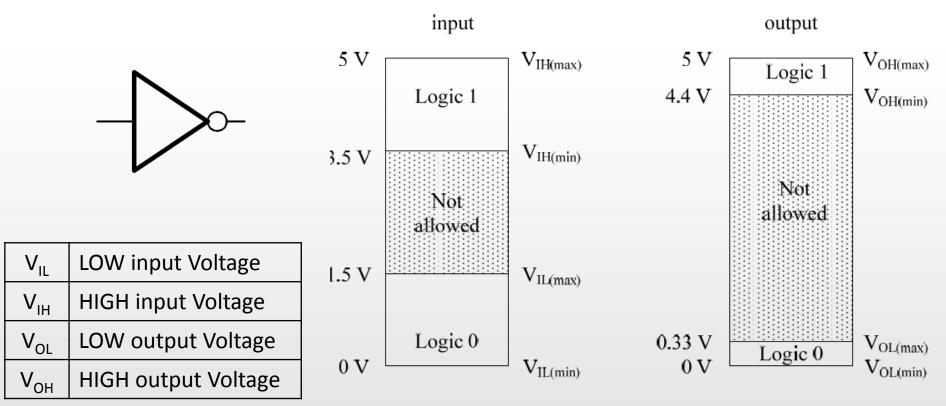

#### **Logic Levels**

|                | TTL                   | CMOS                     |

|----------------|-----------------------|--------------------------|

| Supply voltage | 5V (V <sub>cc</sub> ) | 3 to 15V ( $V_{DD}$ )    |

| Logic 0        | 0 to 0.8V             | 0 to 1/3 $V_{DD}$        |

| Logic 1        | 2V to 5V              | $2/3 V_{DD}$ to $V_{DD}$ |

**TTL Logic Levels**

<u>©UTM</u>

**CMOS Logic Levels**

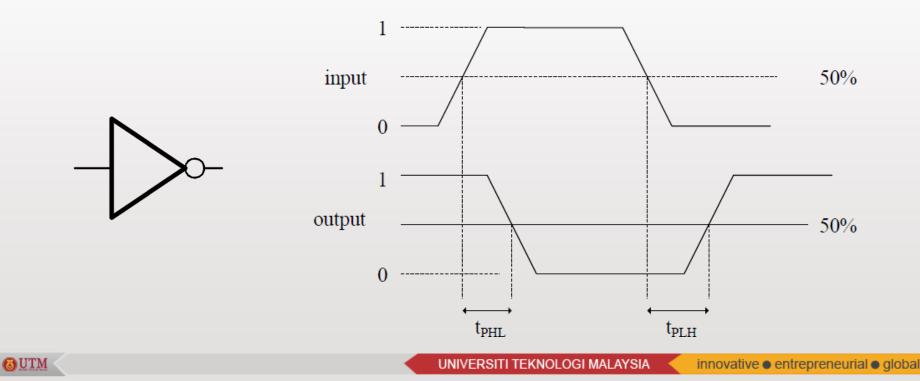

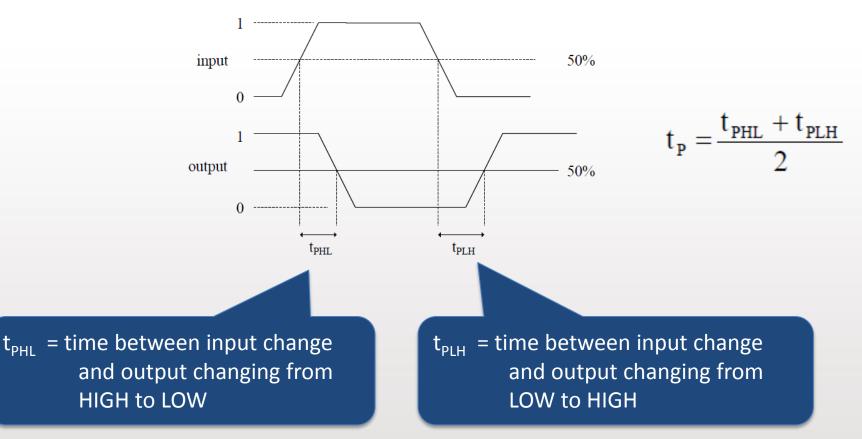

## Propagation Delay

- Logic outputs need time to change from 0 to 1 or 1 to 0.

- Propagation delay is measured at 50%

OUTM

#### **Propagation Delay**

#### **TTL Power Dissipation**

$P_D = V_{CC} \times I_{AVE}$  $I_{AVE} = (I_{CCH} + I_{CCL})/2$

where

V<sub>CC</sub> = supply voltage I<sub>AVE</sub> = average current I<sub>CCH</sub> = current in HIGH state I<sub>CCL</sub> = current in LOW state

#### **Power Dissipation**

$P_{\rm D} = C_L \times (V_{\rm DD}^2/2) \times f$

where

- $V_{DD}$  = supply voltage

- $C_L$  = load capacitance

- f = switching frequency

Power dissipation is dependent on switching activity Power is dissipated only on  $0 \rightarrow 1$  transitions

### **Noise Immunity**

- Noise

- unwanted signal in electrical circuits caused by electromagnetic radiation or power transmission lines

- Noise margin

- A measure of a circuit's ability to tolerate a certain amount of noise

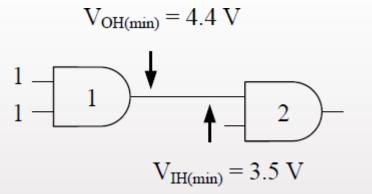

#### **Noise Immunity**

- V<sub>NH</sub> = high level noise margin

- $V_{OH(min)} V_{IH(min)}$

- VNL = low level noise margin

- $V_{IL(max)} V_{OL(min)}$

- Example for 5V CMOS

•

$$V_{\rm NH} = 4.4V - 3.5V = 0.9V$$

#### Fan-out

- Fan-out is the maximum number of load gate inputs that can be connected without adversely affecting the specific operational characteristics of a gate.

- If a gate has a fan-out of 10, then it can drive 10 other similar gates.

- We use the lower of two fan-outs, LOW and HIGH

```

\begin{aligned} & \mathsf{Fan-out}_{\mathsf{LOW}} = \mathsf{I}_{\mathsf{OL}}(\mathsf{max})/\mathsf{I}_{\mathsf{IL}}(\mathsf{max}) \\ & \mathsf{Fan-out}_{\mathsf{HIGH}} = \mathsf{I}_{\mathsf{OH}}(\mathsf{max})/\mathsf{I}_{\mathsf{IH}}(\mathsf{max}) \\ & \mathsf{Fan-out} = \mathsf{min}(\mathsf{fan-out}_{\mathsf{LOW}}, \mathsf{fan-out}_{\mathsf{HIGH}}) \end{aligned}

```

# Thank You!

Helang Ekor Cabang / Black Kite / Milvus migrans di Kuala Gula, Perak

© 2012 Mun'im Zabidi